Edition 1.0 2019-03

# TECHNICAL REPORT

Device embedding assembly technology D PREVIEW

Part 2-7: Guidelines – Accelerated stress testing of passive embedded circuit boards

IEC TR 62878-2-7:2019 https://standards.iteh.ai/catalog/standards/sist/f53bc80c-44b5-4d9e-99c8-65f61a5c9099/iec-tr-62878-2-7-2019

### THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2019 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Tel.: +41 22 919 02 11 info@iec.ch

www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigendum or an amendment might have been published.

### IEC publications search - webstore.iec.ch/advsearchform

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications.

**IEC Just Published - webstore.iec.ch/justpublished**Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and once a month by email.

### IEC Customer Service Centre - webstore iec ch/csc If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer Service Centre: sales@iec.ch.

Electropedia - www.electropedia.org

The world's leading online dictionary on electrotechnology, containing more than 22 000 terminological entries in English and French, with equivalent terms in 16 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

### IEC Glossary - std.iec.ch/glossary

67 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR.

IEC TR 62878-2-7:2019

https://standards.iteh.ai/catalog/standards/sist/153bc80c-44b5-4d9e-99c8 65f61a5c9099/iec-tr-62878-2-7-2019

### IEC TR 62878-2-7

Edition 1.0 2019-03

# TECHNICAL REPORT

Device embedding assembly technology D PREVIEW

Part 2-7: Guidelines – Accelerated stress testing of passive embedded circuit boards

IEC TR 62878-2-7:2019 https://standards.iteh.ai/catalog/standards/sist/f53bc80c-44b5-4d9e-99c8-65f61a5c9099/iec-tr-62878-2-7-2019

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.180; 31.190 ISBN 978-2-8322-6680-9

Warning! Make sure that you obtained this publication from an authorized distributor.

### CONTENTS

| FOREWORD                                                                                                                          | 3  |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 1 Scope                                                                                                                           | 5  |

| 2 Normative references                                                                                                            | 5  |

| 3 Terms and definitions                                                                                                           | 5  |

| 4 Overview of accelerated stress testing of passive embedded circuit boards                                                       | 55 |

| 4.1 Testing under combined stresses                                                                                               | 5  |

| 4.2 Test coupon design                                                                                                            | 6  |

| 5 Test procedure                                                                                                                  | 8  |

| 5.1 General                                                                                                                       | 8  |

| 5.2 Setting test temperature                                                                                                      |    |

| 5.3 Placement of samples on bending tester                                                                                        |    |

| 5.4 Imposing combined stresses                                                                                                    |    |

| 5.5 Evaluation of results                                                                                                         |    |

|                                                                                                                                   |    |

| Annex A (informative) Test coupon design rule                                                                                     |    |

| Annex B (informative) Bending testing                                                                                             | 12 |

| Figure 1 – Testing principalhS.T.A.N.D.A.R.DP.R.E.V.IE.W                                                                          | 6  |

|                                                                                                                                   |    |

| Figure 3 – Test coupon structure                                                                                                  | 7  |

| Figure 4 – Opened and closed sample Figure 4 – Opened and closed sample Figure 4 – Opened and closed sample Figure 62878-2-7:2019 |    |

| Figure 5 _ Bendinghtps//staydards/dsla/catalog/standards/sist/f53bc80c-44b5-4d9e-99c8-                                            | ٥  |

| Figure 6 – Output voltage                                                                                                         | 10 |

| Figure 7 – Cross section of sample after testing                                                                                  |    |

| Figure 8 – Cross section of failed sample                                                                                         |    |

| Figure B.1 – Bending tester in the chamber                                                                                        |    |

| rigure B.1 Bending tester in the chamber                                                                                          | 12 |

| Table 1 – Design information for test coupon                                                                                      | 7  |

| Table 2 – Stack-up information for test coupon                                                                                    |    |

| Table 3 – Coupon testing results                                                                                                  |    |

| Table A.1 – Test coupon design rules                                                                                              |    |

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### DEVICE EMBEDDING ASSEMBLY TECHNOLOGY

## Part 2-7: Guidelines – Accelerated stress testing of passive embedded circuit boards

### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user. Standards.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter. https://standards.itch.ai/catalog/standards/sist/f53bc80c-44b5-4d9e-99c8-

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC TR 62878-2-7, which is a technical report, has been prepared by IEC technical committee 91: Electronics assembly technology.

\_ 4 \_

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 91/1553/DTR   | 91/1559/RVDTR    |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 62878 series, published under the general title *Device embedding* assembly technology, can be found on the IEC website.

Future standards in this series will carry the new general title as cited above. Titles of existing standards in this series will be updated at the time of the next edition.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or ANDARD PREVIEW

- amended.

(standards.iteh.ai)

A bilingual version of this publication may be issued at a later date.

IEC TR 62878-2-7:2019

https://standards.iteh.ai/catalog/standards/sist/f53bc80c-44b5-4d9e-99c8-65f61a5c9099/iec-tr-62878-2-7-2019

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

### DEVICE EMBEDDING ASSEMBLY TECHNOLOGY

# Part 2-7: Guidelines – Accelerated stress testing of passive embedded circuit boards

### 1 Scope

This part of IEC 62878 describes the accelerated stress testing of passive embedded circuit boards. It can be used for screening finished boards, including multilayer and high-density interconnection (HDI) boards. These boards are mainly for mobile devices.

### 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60194, Printed board design, manufacture and assembly - Terms and definitions

Teh STANDARD PREVIEW

## Terms and definitions (standards.iteh.ai)

,

For the purposes of this document, the terms and definitions given in IEC 60194 apply.

https://standards.iteh.ai/catalog/standards/sist/f53bc80c-44b5-4d9e-99c8-

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at http://www.electropedia.org/

- ISO Online browsing platform: available at http://www.iso.org/obp

### 4 Overview of accelerated stress testing of passive embedded circuit boards

### 4.1 Testing under combined stresses

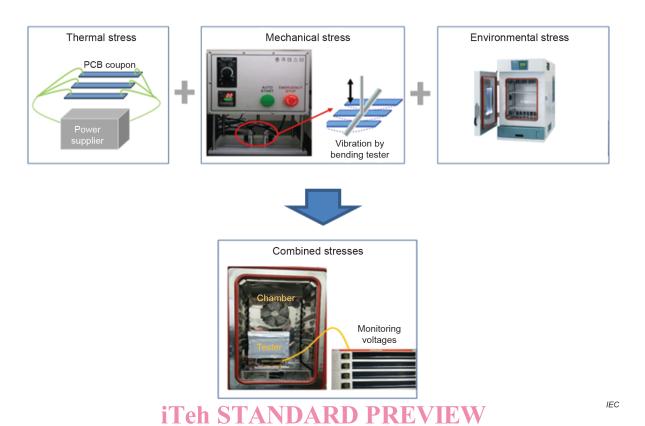

A combined test method has been used to simulate real world conditions. It is a combination of a thermal stress by heating at high temperature, an environmental stress at 85 °C/ 85 % RH, and a mechanical stress with vibration. In order to test specimens under various stresses, a bending tester with heat generating specimens was put into the thermo-hydrostat. The reliability can be checked by monitoring output voltage of the heated sample as shown in Figure 1. The heating temperature is set to 325 °C in order to shorten the testing time to 1 h for boards fabricated with a high temperature of decomposition ( $T_{\rm d}$ ) material ( $T_{\rm d}$  > 350 °C). The testing can be done at 305 °C for 1,5 h if material with a lower  $T_{\rm d}$  is used.

### Figure 1-Testing principal

### 4.2 Test coupon design

### IEC TR 62878-2-7:2019

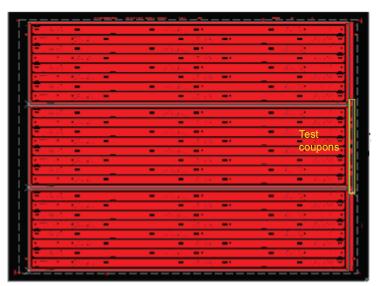

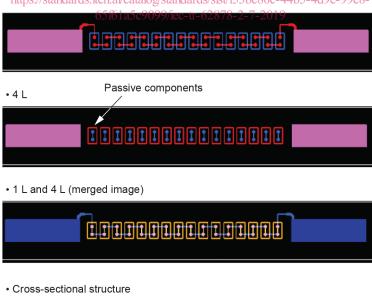

Four test coupons are built in a test area of passive embedded circuit board panel as shown in Figure 2. Each test coupon has circuits connecting embedded passives, as shown in Figure 3, that act as heating circuits as well. They are fabricated in accordance with the design rules in Annex A. The design and layer specifications are shown in Tables 1 and 2. The circuits of the top and the bottom layers are the same.

- ★ Test panel information

- Size: 610 mm × 450 mm

- Number of layer: 4 L

IEC

Figure 2 - Embedded circuit board panel with test coupons

Table 1 – Design information for test coupon

| Line width                           | 100 μm         |

|--------------------------------------|----------------|

| Via pad                              | 350 μm         |

| Distance between embedded components | 450            |

| Ground connection size               | 7,28 mm × 2 mm |

| Coupon size                          | 35 mm × 5 mm   |

Table 2 - Stack-up information for test coupon

| Layer                     | Thickness (µm)        |

|---------------------------|-----------------------|

| Solder resistor           | 20                    |

| Circuits (copper)         | 30                    |

| Dielectric (prepreg)      | 60                    |

| Circuits (copper)         | 35                    |

| Dielectric (FR4 core)     | 250                   |

| Circuits (copper)         | 35                    |

| Dielectric (prepreg)      | 60                    |

| Circuits (copper) DARD    | PREVI <sub>30</sub> W |

| Solder resisten dards.ite | <b>h.ai</b> ) 20      |

| Total IEC TR (2878-2-720  | 540 ± 54              |

https://standards.iteh.ai/catalog/standards/sist/f53bc80c-44b5-4d9e-99c8-

Figure 3 – Test coupon structure