Edition 2.0 2022-03

# INTERNATIONAL **STANDARD**

# **NORME** INTERNATIONALE

Semiconductor devices – Mechanical and climatic test methods – Part 28: Electrostatic discharge (ESD) sensitivity testing - Charged device model (CDM) - device level

(standards.iteh.ai)

Dispositifs à semiconducteurs - Méthodes d'essais mécaniques et climatiques -IEC 60749-28:2022

Partie 28: Essai de sensibilité aux décharges électrostatiques (DES) - Modèle de dispositif chargé (CDM) 25 niveau du dispositif c-60749-28-2022

# THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2022 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Secretariat Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch CH-1211 Geneva 20 www.iec.ch

Switzerland

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigendum or an amendment might have been published.

#### IEC publications search - webstore.iec.ch/advsearchform

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee, ...). It also gives information on projects, replaced and withdrawn publications.

### IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and once a month by email.

#### IEC Products & Services Portal - products.iec.ch

Discover our powerful search engine and read freely all the publications previews. With a subscription you will always have access to up to date content tailored to your needs.

#### Electropedia - www.electropedia.org

The world's leading online dictionary on electrotechnology, containing more than 22 300 terminological entries in English and French, with equivalent terms in 19 additional languages. Also known as the International Electrotechnical Vocabulary

## IEC Customer Service Centre - webstore.iec.ch/csc 60749-28.2022

If you wish to give us your feedback on this publication of alog/standards/sist/07a14260-need further assistance, please contact the Customer Service

Centre: sales@iec.ch. d120-425c-9885-964f8a811dfd/iec-60749-28-2022

### A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

#### A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l'édition la plus récente, un corrigendum ou amendement peut avoir été publié.

## Recherche de publications IEC - webstore.iec.ch/advsearchform

La recherche avancée permet de trouver des publications IEC en utilisant différents critères (numéro de référence, texte, comité d'études, ...). Elle donne aussi des informations sur les projets et les publications remplacées ou retirées.

#### IEC Just Published - webstore.iec.ch/justpublished

Restez informé sur les nouvelles publications IEC. Just Published détaille les nouvelles publications parues. Disponible en ligne et une fois par mois par email.

## Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions contactez-nous: sales@iec.ch.

### IEC Products & Services Portal - products.iec.ch

Découvrez notre puissant moteur de recherche et consultez gratuitement tous les aperçus des publications. Avec un abonnement, vous aurez toujours accès à un contenu à jour adapté à vos besoins.

### Electropedia - www.electropedia.org

Le premier dictionnaire d'électrotechnologie en ligne au monde, avec plus de 22 300 articles terminologiques en anglais et en français, ainsi que les termes équivalents dans 19 langues additionnelles. Egalement appelé Vocabulaire Electrotechnique International (IEV) en ligne.

Edition 2.0 2022-03

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

## iTeh STANDARD

Semiconductor devices – Mechanical and climatic test methods – Part 28: Electrostatic discharge (ESD) sensitivity testing – Charged device model (CDM) – device level (Standards.iteh.ai)

Dispositifs à semiconducteurs – Méthodes d'essais mécaniques et climatiques – <u>IEC 60749-28:2022</u>

Partie 28: Essai de sensibilité aux décharges électrostatiques (DES) – Modèle de dispositif chargé (CDM) inveau du dispositif c-60749-28-2022

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

ICS 31.080.01 ISBN 978-2-8322-1082-9

Warning! Make sure that you obtained this publication from an authorized distributor. Attention! Veuillez vous assurer que vous avez obtenu cette publication via un distributeur agréé.

## CONTENTS

| FC | DREWO | RD                                                                             | 6  |

|----|-------|--------------------------------------------------------------------------------|----|

| IN | TRODU | ICTION                                                                         | 8  |

| 1  | Scop  | e                                                                              | 9  |

| 2  | Norm  | native references                                                              | 9  |

| 3  | Term  | s and definitions                                                              | 9  |

| 4  | Requ  | iired equipment                                                                | 10 |

|    | 4.1   | CDM ESD tester                                                                 | 10 |

|    | 4.1.1 |                                                                                |    |

|    | 4.1.2 | Current-sensing element                                                        | 11 |

|    | 4.1.3 | Ground plane                                                                   | 11 |

|    | 4.1.4 | Field plate/field plate dielectric layer                                       | 11 |

|    | 4.1.5 | Charging resistor                                                              | 11 |

|    | 4.2   | Waveform measurement equipment                                                 | 12 |

|    | 4.2.1 | General                                                                        | 12 |

|    | 4.2.2 | Cable assemblies                                                               | 12 |

|    | 4.2.3 |                                                                                |    |

|    | 4.2.4 | 1 1 ,                                                                          |    |

|    | 4.3   | Verification modules (metal discs).  Capacitance meter.                        | 12 |

|    | 4.4   |                                                                                |    |

|    | 4.5   | Ohmmeter (Standards iteh ai)                                                   | 12 |

| 5  |       | odic tester qualification, waveform records, and waveform verification rements |    |

|    | 5.1   | Overview of required CDM tester evaluations:                                   | 13 |

|    | 5.2   | Waveformtcapture_nhardwareh.ai/catalog/standards/sist/07a14260-                | 13 |

|    | 5.3   | Waveform capture setup885-9b4f8a811dfd/iec-60749-28-2022                       | 13 |

|    | 5.4   | Waveform capture procedure                                                     |    |

|    | 5.5   | CDM tester qualification/requalification procedure                             | 14 |

|    | 5.5.1 | CDM tester qualification/requalification procedure                             | 14 |

|    | 5.5.2 | Conditions requiring CDM tester qualification/requalification                  | 14 |

|    | 5.5.3 | 1 GHz oscilloscope correlation with high bandwidth oscilloscope                | 14 |

|    | 5.6   | CDM tester quarterly and routine waveform verification procedure               | 15 |

|    | 5.6.1 | Quarterly waveform verification procedure                                      | 15 |

|    | 5.6.2 | ·                                                                              |    |

|    | 5.7   | Waveform characteristics                                                       | 15 |

|    | 5.8   | Documentation                                                                  | 17 |

|    | 5.9   | Procedure for evaluating full CDM tester charging of a device                  | 17 |

| 6  | CDM   | ESD testing requirements and procedures                                        | 18 |

|    | 6.1   | Tester and device preparation                                                  | 18 |

|    | 6.2   | Test requirements                                                              |    |

|    | 6.2.1 | Test temperature and humidity                                                  | 18 |

|    | 6.2.2 |                                                                                |    |

|    | 6.3   | Test procedures                                                                |    |

|    | 6.4   | CDM test recording / reporting guidelines                                      |    |

|    | 6.4.1 | 3                                                                              |    |

|    | 6.4.2 | 1 0                                                                            |    |

|    | 6.5   | Testing of Devices in Small Packages                                           | 19 |

| 7 CDM classification criteria                                                                                                    | 20       |

|----------------------------------------------------------------------------------------------------------------------------------|----------|

| Annex A (normative) Verification module (metal disc) specifications and cleaning guidelines for verification modules and testers | 21       |

| A.1 Tester verification modules and field plate dielectric                                                                       | 21       |

| A.2 Care of verification modules                                                                                                 | 21       |

| Annex B (normative) Capacitance measurement of verification modules (metal discs) sitting on a tester field plate dielectric     | 22       |

| Annex C (normative) Testing of small package integrated circuits and discrete semiconductors (ICDS)                              | 23       |

| C.1 Testing rationale                                                                                                            | 23       |

| C.2 Procedure for Determining $C_{\sf Small}$                                                                                    | 23       |

| C.3 ICDS Technology requirements                                                                                                 | 24       |

| Annex D (informative) CDM test hardware and metrology improvements                                                               | 25       |

| Annex E (informative) CDM tester electrical schematic                                                                            | 27       |

| Annex F (informative) Sample oscilloscope setup and waveform                                                                     | 28       |

| F.1 General                                                                                                                      |          |

| F.2 Settings for the 1 GHz bandwidth oscilloscope                                                                                | 28       |

| F.3 Settings for the high-bandwidth oscilloscope                                                                                 | 28       |

| F.4 SetupF.5 Sample waveforms from a 1 GHz oscilloscope                                                                          | 28       |

| F.5 Sample waveforms from a 1 GHz oscilloscope                                                                                   | 28       |

| F.6 Sample waveforms from an 8 GHz oscilloscope /                                                                                | 29       |

| Annex G (informative) Field-induced CDM tester discharge procedures                                                              |          |

| G.1 General (standards.itch.ai) G.2 Single discharge procedure                                                                   | 31       |

| G.2 Single discharge procedure                                                                                                   | 31       |

| G.3 Dual discharge procedure                                                                                                     | 31       |

| Annex H (informative) Waveform verification procedures                                                                           | 33       |

| H.1 Factor/offset adjustment method f8a811dfd/jec-60749-28-2022                                                                  | 33       |

| H.2 Software voltage adjustment method                                                                                           |          |

| H.3 Example parameter recording tables                                                                                           | 38       |

| Annex I (informative) Determining the appropriate charge delay for full charging of a large module or device                     | 40       |

| I.1 General                                                                                                                      | 40       |

| I.2 Procedure for charge delay determination                                                                                     | 40       |

| Annex J (informative) Electrostatic discharge (ESD) sensitivity testing direct contact charged device model (DC-CDM)             | 42       |

| J.1 General                                                                                                                      | 42       |

| J.2 Standard test module                                                                                                         | 42       |

| J.3 Test equipment (CDM simulator)                                                                                               |          |

| J.3.1 Test equipment design                                                                                                      |          |

| J.3.2 DUT (device under test) support                                                                                            |          |

| J.3.3 Metal bar/board                                                                                                            |          |

| J.3.4 Equipment setup                                                                                                            |          |

| J.4 Verification of test equipment                                                                                               |          |

| J.4.1 General description of verification test equipment                                                                         |          |

| J.4.2 Instruments for measurement                                                                                                |          |

| J.4.3 Verification of test equipment, using a current probe                                                                      |          |

| I.5.1 Initial measurement                                                                                                        | 40<br>46 |

| J.5.2 Tests                                                                                                                                                             | 47                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| J.5.3 Intermediate and final measurement                                                                                                                                | 47                          |

| J.6 Failure criteria                                                                                                                                                    | 47                          |

| J.7 Classification criteria                                                                                                                                             | 47                          |

| J.8 Summary                                                                                                                                                             | 47                          |

| Bibliography                                                                                                                                                            | 49                          |

|                                                                                                                                                                         |                             |

| Figure 1 – Simplified CDM tester hardware schematic                                                                                                                     |                             |

| Figure 2 – CDM characteristic waveform and parameters                                                                                                                   |                             |

| Figure E.1 – Simplified CDM tester electrical schematic                                                                                                                 |                             |

| Figure F.1 – 1 GHz TC 500, small verification module                                                                                                                    |                             |

| Figure F.2 – 1 GHz TC 500, large verification module                                                                                                                    |                             |

| Figure F.3 – 8 GHz TC 500, small verification module (oscilloscope adjusts for attenuation)                                                                             |                             |

| Figure F.4 – GHz TC 500, large verification module (oscilloscope adjusts for attenuation)                                                                               | 30                          |

| Figure G.1 – Single discharge procedure (field charging, $I_{CDM}$ Pulse, and slow discharge)                                                                           |                             |

| Figure G.2 – Dual discharge procedure (field charging, 1st ICDM pulse, no fie                                                                                           |                             |

|                                                                                                                                                                         |                             |

| ICDM pulse)                                                                                                                                                             |                             |

| Figure H.1 – An example of a waveform verification flow for qualification and checks using the factor/offset adjustment method                                          | <sub>l</sub> uarterly<br>34 |

| Figure H.2 – An example of a waveform verification flow for the routine checks the factor/offset adjustment method                                                      |                             |

| Figure H.3 – Example of average $I_{\mbox{peak}}$ for the large Verification module – high bandwidth oscilloscopes://standards.iteh.ai/catalog/standards/sist/07a14260- | า                           |

| bandwidth oscilloscopes://standards.iteh.ai/catalog/standards/sist/07a14260-                                                                                            | 36                          |

| Figure H.4 – An example of a waveform verification flow for qualification and checks using the software voltage adjustment method                                       | quarterly<br>37             |

| Figure H.5 – An example of a waveform verification flow for the routine checks the software voltage adjustment method                                                   | s using<br>38               |

| Figure I.1 – An example characterization of charge delay vs. $I_p$                                                                                                      | 41                          |

| Figure J.1 – Examples of discharge circuit where the discharge is caused by the switch                                                                                  |                             |

| Figure J.2 – Verification test equipment for measuring the discharge current fl                                                                                         |                             |

| the metal bar/board from the standard test module                                                                                                                       |                             |

| Figure J.3 – Current waveform                                                                                                                                           | 44                          |

| Figure J.4 – Measurement circuit for verification method using a current probe                                                                                          | 46                          |

| Table 1 – CDM waveform characteristics for a 1 GHz bandwidth oscilloscope                                                                                               | 16                          |

| Table 2 – CDM waveform characteristics for a high-bandwidth (≥ 6 GHz) oscill                                                                                            | oscope16                    |

| Table 3 – CDM ESDS device classification levels                                                                                                                         |                             |

| Table A.1 – Specification for CDM tester verification modules (metal discs)                                                                                             |                             |

| Table H.1 – Example waveform parameter recording table for the factor/offset                                                                                            |                             |

| adjustment method                                                                                                                                                       |                             |

| Table H.2 – Example waveform parameter recording table for the software vol adjustment method                                                                           |                             |

| Table J.1 – Dimensions of the standard test modules                                                                                                                     |                             |

|                                                                                                                                                                         |                             |

| _ |  |

|---|--|

| F |  |

|   |  |

| Table J.2 – Specified current waveform                                                       | 45 |

|----------------------------------------------------------------------------------------------|----|

| Table J.3 – Range of peak current $I_{p1}$ for test equipment                                | 45 |

| Table J.4 – Specification of peak current $I_{D1}$ for the current probe verification method | 46 |

# iTeh STANDARD PREVIEW (standards.iteh.ai)

IEC 60749-28:2022

https://standards.iteh.ai/catalog/standards/sist/07a14260-d120-425c-9885-9b4f8a811dfd/iec-60749-28-2022

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

## SEMICONDUCTOR DEVICES – MECHANICAL AND CLIMATIC TEST METHODS –

## Part 28: Electrostatic discharge (ESD) sensitivity testing – Charged device model (CDM) – device level

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

IEC 60749-28 has been prepared by IEC technical committee 47: Semiconductor devices, in collaboration with IEC technical committee 101: Electrostatics. It is an International Standard.

ANSI/ESDA/JEDEC JS-002-2018 has served as a basis for the elaboration of this standard. It is used with permission of the copyright holders, ESD Association and JEDEC Solid state Technology Association. ANSI/ESDA/JEDEC JS-002-2018 describes the field-induced (FI) method. An alternative, the direct contact (DC) method (not based on JS-002-2018), is described in Annex J.

This second edition cancels and replaces the first edition published in 2017. This edition constitutes a technical revision.

This edition includes the following significant technical changes with respect to the previous edition:

- a) a new subclause and annex relating to the problems associated with CDM testing of integrated circuits and discrete semiconductors in very small packages;

- b) changes to clarify cleaning of devices and testers.

The text of this International Standard is based on the following documents:

| Draft        | Report on voting |

|--------------|------------------|

| 47/2746/FDIS | 47/2754/RVD      |

Full information on the voting for its approval can be found in the report on voting indicated in the above table.

The language used for the development of this International Standard is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available at <a href="https://www.iec.ch/members\_experts/refdocs">www.iec.ch/members\_experts/refdocs</a>. The main document types developed by IEC are described in greater detail at <a href="https://www.iec.ch/standardsdev/publications">www.iec.ch/standardsdev/publications</a>.

A list of all parts in the IEC 60749 series, published under the general title *Semiconductor* devices – Mechanical and climatic test methods, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data related to the specific document. At this date, the document will be

- reconfirmed,

- (standards.iteh.ai)

- withdrawn,

- replaced by a revised edition, or IEC 60749-28:2022

- amended. https://standards.iteh.ai/catalog/standards/sist/07a14260-d120-425c-9885-9b4f8a811dfd/iec-60749-28-2022

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

### INTRODUCTION

The earliest electrostatic discharge (ESD) test models and standards simulate a charged object approaching a device and discharging through the device. The most common example is IEC 60749-26, the human body model (HBM). However, with the increasing use of automated device handling systems, another potentially destructive discharge mechanism, the charged device model (CDM), becomes increasingly important. In the CDM, a device itself becomes charged (e.g. by sliding on a surface (tribocharging) or by electric field induction) and is rapidly discharged (by an ESD event) as it closely approaches a conductive object. A critical feature of the CDM is the metal-metal discharge, which results in a very rapid transfer of charge through an air breakdown arc. The CDM test method also simulates metal-metal discharges arising from other similar scenarios, such as the discharging of charged metal objects to devices at different potential.

Accurately quantifying and reproducing this fast metal-metal discharge event is very difficult, if not impossible, due to the limitations of the measuring equipment and its influence on the discharge event. The CDM discharge is generally completed in a few nanoseconds, and peak currents of tens of amperes have been observed. The peak current into the device will vary considerably depending on a large number of factors, including package type and parasitics. The typical failure mechanism observed in MOS devices for the CDM model is dielectric damage, although other damage has been noted.

The CDM charge voltage sensitivity of a given device is package dependent. For example, the same integrated circuit (IC) in a small area package can be less susceptible to CDM damage at a given voltage compared to that same IC in a package of the same type with a larger area. It has been shown that CDM damage susceptibility correlates better to peak current levels than charge voltage.

(standards.iteh.ai)

<u>IEC 60749-28:2022</u> https://standards.iteh.ai/catalog/standards/sist/07a14260-d120-425c-9885-9b4f8a811dfd/iec-60749-28-2022

## SEMICONDUCTOR DEVICES – MECHANICAL AND CLIMATIC TEST METHODS –

## Part 28: Electrostatic discharge (ESD) sensitivity testing – Charged device model (CDM) – device level

## 1 Scope

This part of IEC 60749 establishes the procedure for testing, evaluating, and classifying devices and microcircuits according to their susceptibility (sensitivity) to damage or degradation by exposure to a defined field-induced charged device model (CDM) electrostatic discharge (ESD). All packaged semiconductor devices, thin film circuits, surface acoustic wave (SAW) devices, opto-electronic devices, hybrid integrated circuits (HICs), and multi-chip modules (MCMs) containing any of these devices are to be evaluated according to this document. To perform the tests, the devices are assembled into a package similar to that expected in the final application. This CDM document does not apply to socketed discharge model testers. This document describes the field-induced (FI) method. An alternative, the direct contact (DC) method, is described in Annex J.

The purpose of this document is to establish a test method that will replicate CDM failures and provide reliable, repeatable CDM ESD test results from tester to tester, regardless of device type. Repeatable data will allow accurate classifications and comparisons of CDM ESD sensitivity levels.

(standards.iteh.ai)

#### 2 Normative references

There are no normative references in this document. https://standards.iten.ai/catalog/standards/sist/07a14260-d120-425c-9885-9b4f8a811dfd/iec-60749-28-2022

#### 3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at http://www.electropedia.org/

- ISO Online browsing platform: available at http://www.iso.org/obp

#### 3.1

#### **CDM ESD**

charged device model electrostatic discharge

electrostatic discharge (ESD) using the charged device model (CDM) to simulate the actual discharge event that occurs when a charged device is quickly discharged to another object at a lower electrostatic potential through a single pin or terminal

### 3.2

#### **CDM ESD tester**

charged device model electrostatic discharge tester equipment that simulates the device level CDM ESD event using the non-socketed test method

Note 1 to entry: "Equipment" is referred to as "tester" in this document.

#### 3.3

### $C_{\mathsf{Small}}$

device to CDM field plate capacitance for an integrated circuit or discrete semiconductor at or below which it has been determined that CDM testing is not required if specified conditions are met

#### 3.4

#### dielectric layer

thin insulator placed atop the field plate used to separate the device from the field plate

#### 3.5

#### field plate

conductive plate used to elevate the potential of the device under test (DUT) by capacitive coupling

Note 1 to entry: See Figure 1.

#### 3.6

#### ground plane

conductive plate used to complete the circuitry for grounding/discharging the DUT

Note 1 to entry: See Figure 1.

#### 3.7

## iTeh STANDARD

### software voltage

user/operator-entered voltage that, when combined with the scale factor or offset, sets the actual field plate voltage on the system in order to achieve the waveform parameters

Note 1 to entry: Waveform parameters are defined in Table 1 or Table 2. 21

3.8

### test condition

IEC 60749-28:2022

https://standards.iteh.ai/catalog/standards/sist/07a14260-tester plate voltage that meets the waveform parameter conditions 2022

Note 1 to entry: The waveform parameter conditions are found in a particular column of Table 1 and Table 2.

### 4 Required equipment

#### 4.1 CDM ESD tester

#### 4.1.1 General

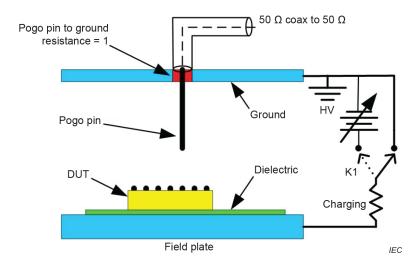

Figure 1 represents the hardware schematic for a CDM tester setup to conduct field-induced CDM ESD testing assuming the use of a resistive current probe. The DUT may be an actual device or it may be one of the two verification modules (metal discs) described in Annex A. The pogo pin shall be connected to the ground plane with a 1  $\Omega$  current path with a minimum bandwidth (BW) of 9 gigahertz (GHz). The 1  $\Omega$  pogo pin to ground connection of the resistive current sensor may be a parallel combination of a 1  $\Omega$  resistor between the pogo pin and the ground plane, and the 50  $\Omega$  impedance of the oscilloscope and its coaxial cable. In Figure 1, K1 is the switch between charging the field plate and grounding the field plate. The CDM ESD testers used within the context of this document shall meet the waveform characteristics specified in Figure 2, and Table 1 and Table 2, without additional passive or active devices, such as ferrites, in the probe's assembly.

Figure 1 - Simplified CDM tester hardware schematic

When constructing the test equipment, the parasitics in the charge and discharge paths should be minimized since the resistance inductance-capacitance (RLC) parasitics in the equipment greatly influence the test results.

For existing equipment, it is recommended to contact qualified service personnel to determine compliance to this document upon removal of ferrite components.

## 4.1.2 Current-sensing element PREV

A current-sensing element shall be incorporated into the ground plane. The resistance of this element shall have a value of  $(1,0 \pm 10 \%)~\Omega$ . A resistor, as specified in 4.1.1, shall be used as the current-sensing element. The value of resistance (including the 50  $\Omega$  cable/oscilloscope termination) shall be measured using an ohimmeter as described in 4.5. The resistance value shall be used to calculate/the first peak current log/standards/sist/07a14260-

d120-425c-9885-9b4f8a811dfd/iec-60749-28-2022

The current-sensing element shall have a minimum frequency response of 9 GHz (specified by a maximum roll-off of 3 dB at 9 GHz).

### 4.1.3 Ground plane

The probe assembly shall contain a square ground plane with the probe pin centred within it as shown in Figure 1. The dimensions of the ground plane shall be  $63.5 \text{ mm} \times 63.5 \text{ mm} \pm 6.35 \text{ mm}$  (2.5 inches  $\times$  2.5 inches  $\pm$  0.25 inches).

## 4.1.4 Field plate/field plate dielectric layer

The field plate shall have a surface flatness to vary no more than  $\pm$  0,127 mm (0,005 inches). The field plate dielectric layer should be made with an FR4 or similar epoxy-glass material. For FR4, the thickness and thickness tolerance of this dielectric layer should be 0,381 mm  $\pm$  0,0254 mm (0,015 inches  $\pm$  0,001 inches) in order to result in a capacitance measurement (as specified in normative Annex B) in the range specified in Table A.1.

If a different material is used, the material thickness is chosen to result in a capacitance measurement in the range specified in Table A.1.

### 4.1.5 Charging resistor

The charging resistor shown in Figure 1 shall nominally be 100 M $\Omega$  or greater.

Resistor values higher than 100 M $\Omega$  may be used, but this may not allow very large devices (refer to 5.9 and Annex I) to charge fully before being discharged by the probe assembly. This effect can be overcome by adding a delay between discharges in the CDM tester programming software. If using a resistor greater than 100 M $\Omega$ , it is recommended that the tester or the device itself be characterized to determine if a delay is needed for discharging large devices. A procedure for this large device delay characterization is given in Annex I.

#### 4.2 Waveform measurement equipment

#### 4.2.1 General

The CDM waveform measurement equipment shall consist of the following components.

#### 4.2.2 Cable assemblies

Cable assemblies with combined internal tester cable and external cable total loss of no more than 2 dB at frequencies up to 5 GHz and a nominal 50  $\Omega$  impedance.

#### 4.2.3 Equipment for high-bandwidth waveform measurement

#### 4.2.3.1 High-bandwidth oscilloscope

An oscilloscope or transient digitizer with a minimum real-time (single shot) 3 dB BW of at least 6 GHz and ≥ 20 gigasample/s sampling rate with a nominal 50  $\Omega$  input impedance.

#### 4.2.3.2 **Attenuator**

A 20 dB attenuator with a precision of ±0,5 dB, at least 12 GHz BW, and an impedance standards.iteh.ai) of 50  $\Omega$  ± 5,0  $\Omega$ .

#### 4.2.4 Equipment for 1.0 GHz waveform measurement

IEC 60749-28:2022

#### 1 GHz oscilloscope ards.iteh.ai/catalog/standards/sist/07a14260-4.2.4.1

An oscilloscope or transient digitizer with a real-time (single shot) 3 dB BW of 1 GHz with a nominal 50  $\Omega$  input impedance. The sampling rate shall be  $\geq$  5 gigasample/s.

NOTE The user has the option of using a higher BW oscilloscope and using a hardware or software filter to produce a bandwidth and sampling rate equivalent to that specified in 4.2.4.1.

#### 4.2.4.2 **Attenuator**

A 20 dB attenuator with a precision of  $\pm$  0.5 dB, at least 4 GHz BW, and an impedance of 50  $\Omega$ ± 5 Ω.

#### 4.3 Verification modules (metal discs)

The large verification module shall have a capacitance of (55 ± 5 %) pF and the small verification module shall have a capacitance of (6,8 ± 5 %) pF. Refer to normative Annex A for information on the verification module physical dimensions and normative Annex B for information on the capacitance measurement procedure.

#### 4.4 Capacitance meter

Capacitance meter with a resolution of 0,2 pF, a measurement accuracy of 3 %, and a measurement frequency of 1,0 MHz as described in normative Annex B.

#### 4.5 Ohmmeter

The ohmmeter used to measure the resistance of the resistive probe shall be capable of measuring to an accuracy of 0,01  $\Omega$ . Use of Kelvin 4-wire connections is recommended.

## 5 Periodic tester qualification, waveform records, and waveform verification requirements

### 5.1 Overview of required CDM tester evaluations

The CDM tester shall be qualified, re-qualified, and periodically verified as described in 5.5 and 5.6.

NOTE 1 Dielectric layers, ground planes (ground plates), the coaxial discharging resistor (probe), the distance between the ground plane and the field plate, the verification modules and the discharge contacts (e.g., pogo pins) are key elements of the tester construction. Any change to these elements necessitates a waveform verification.

NOTE 2 Changes in the shape of the discharge pulse, even though they can still be within specification, can indicate degradation of the discharge path.

### 5.2 Waveform capture hardware

Waveform capture requires the following instrumentation and tester set voltage procedure:

- an oscilloscope as specified in 4.2;

- an attenuator and cable assembly as defined in 4.2;

- verification modules (as described in 4.3) with the dimensions and attributes listed in normative Annex A and the method of measurement listed in normative Annex B.

## 5.3 Waveform capture setupeh STANDARD

The waveform capture setup shall be carried out as follows:

- a) Clean the verification modules. Avoid skin contact with the modules prior to, and during testing. A recommended procedure is described in normative Annex A.

- b) Using an alcohol wipe, clean the discharge probe and the field charge plate on which the device is placed to remove any surface contamination that could result in charge loss. Ensure the pogo pin is free of particulates.

- c) Attach the appropriate 20 dB attenuator as described in 4.2.3.2 to the oscilloscope. Attach one end of the external cable assembly, as described in 4.2.2, to the attenuator and the other end to the CDM tester. Verify all connections in the measurement chain are tight.

See informative Annex F for an example of oscilloscope settings and captured waveforms.

#### 5.4 Waveform capture procedure

The waveform capture procedure shall be carried out as follows:

- a) Place the verification module to be used on the field plate dielectric, ensuring intimate contact between the field plate dielectric and verification module.

- b) Set the potential of the field plate to the needed voltage for the test condition being run.

- c) Align the ground pin to approximately the centre of the verification module.

- d) Either the single discharge or dual discharge method as described in Clause G.2 or Clause G.3 respectively can be used, but the discharge method chosen should be consistent with how products will be tested. When using the dual discharge method, waveforms for positive and negative pulses require a change in the oscilloscope trigger conditions to capture only positive or negative pulses.

- e) Discharge the verification module at least ten times at the polarity being verified.

- f) Observe at least ten successive waveforms during the set of discharges above and record the average waveform parameters for  $I_{\rm p}$ ,  $T_{\rm r}$ , full width at half maximum (FWHM), and Ip2 for this group of waveforms as shown in Figure 2.