Edition 1.0 2022-04

# **TECHNICAL REPORT**

Device embedding assembly technology –

Part 2-9: Guidelines – Concept of USSO Level in the electronic assembly technology industries (standards.iteh.ai)

IEC TR 62878-2-9:2022

https://standards.iteh.ai/catalog/standards/sist/882cdbb5fbf0-48fe-aecf-e6f2aed32618/iec-tr-62878-2-9-2022

### THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2022 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

**IEC Secretariat** 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Tel.: +41 22 919 02 11 info@iec.ch

www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigendum or an amendment might have been published.

#### IEC publications search - webstore.iec.ch/advsearchform

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee, ...). It also gives information on projects, replaced and withdrawn publications.

IEC Just Published - webstore.iec.ch/justpublished Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and once a month by email.

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or If you wish to give us your feedback on this publication of need further assistance, please contact the Customer Service CS.11eh.a1 Centre: sales@iec.ch.

#### IEC Products & Services Portal - products.iec.ch

Discover our powerful search engine and read freely all the publications previews. With a subscription you will always have access to up to date content tailored to your needs.

#### Electropedia - www.electropedia.org

The world's leading online dictionary on electrotechnology, containing/more than 22 300 terminological entries in English and French, with equivalent terms in 19 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

IEC TR 62878-2-9:2022

https://standards.iteh.ai/catalog/standards/sist/882cdbb5fbf0-48fe-aecf-e6f2aed32618/iec-tr-62878-2-9-2022

## IEC TR 62878-2-9

Edition 1.0 2022-04

# TECHNICAL REPORT

## iTeh STANDARD

Device embedding assembly technology — Part 2-9: Guidelines – Concept of VISSO Level in the electronic assembly technology industries (standards.iteh.ai)

IEC TR 62878-2-9:2022 https://standards.iteh.ai/catalog/standards/sist/882cdbb5-fbf0-48fe-aecf-e6f2aed32618/iec-tr-62878-2-9-2022

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.180; 31.190 ISBN 978-2-8322-1104-2

Warning! Make sure that you obtained this publication from an authorized distributor.

## CONTENTS

| FOREWORD                                                                                                     | 3       |

|--------------------------------------------------------------------------------------------------------------|---------|

| INTRODUCTION                                                                                                 | 5       |

| 1 Scope                                                                                                      | 6       |

| 2 Normative references                                                                                       | 6       |

| 3 Terms                                                                                                      |         |

| 4 Historical Concept of Jisso (JISSO)                                                                        |         |

| 4.1 Some examples of terms on Jisso/JISSO used in the p                                                      | ast6    |

| 4.2 JISSO level versus Packaging Level (Interconnecting I                                                    | _evel)8 |

| 4.2.1 JISSO Level (typical)                                                                                  | 8       |

| 4.2.2 Packaging Level                                                                                        | 8       |

| 5 Concept of typical terms and description on JISSO Level                                                    | g       |

| 5.1 JISSO/Jisso                                                                                              | g       |

| 5.2 JISSO Level 0 – Intellectual information                                                                 | 10      |

| 5.3 JISSO Product Level 1 – Electronic element                                                               | 10      |

| 5.4 JISSO Product Level 2 – Electronic package                                                               | 12      |

| 5.5 JISSO Product Level 3 – Electronic module                                                                |         |

| <ul> <li>JISSO Product Level 4 Electronic unit</li> <li>JISSO Product Level 5 – Electronic system</li> </ul> | 13      |

|                                                                                                              |         |

| Bibliography                                                                                                 | 15      |

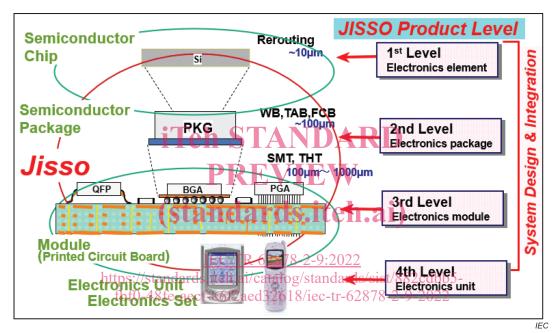

| Figure 1 – Concept of Jisso/JISSOndards.iteh.ai                                                              |         |

| Figure 2 – Relation between JISSO Level versus Packaging Leve                                                |         |

| Figure 3 – JISSO Level Concept (1) preliminarily introduced by J                                             |         |

| Figure 4 – JISSO Lever Concept (2) iteh.ai/catalog/standards/sist/                                           |         |

| Figure 5 – Examples of JISSO Product Level 1 – Electronic elem                                               |         |

| •                                                                                                            |         |

| Figure 6 – Examples of JISSO Product Level 2 – Electronic pack                                               |         |

| Figure 7 – Examples of JISSO Product Level 3 – Electronic modu                                               |         |

| Figure 8 – Example of JISSO Product Level 4 – Electronic unit                                                |         |

| Figure 9 - Examples of JISSO product Level 5 - Electronic syste                                              | m 14    |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### DEVICE EMBEDDING ASSEMBLY TECHNOLOGY -

## Part 2-9: Guidelines – Concept of JISSO Level in the electronic assembly technology industries

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication. 1882cdbb5-

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

IEC TR 62878-2-9 has been prepared by IEC technical committee 91: Electronics assembly technology. It is a Technical Report.

The text of this Technical Report is based on the following documents:

| Draft       | Report on voting |

|-------------|------------------|

| 91/1703/DTR | 91/1769/RVDTR    |

Full information on the voting for its approval can be found in the report on voting indicated in the above table.

The language used for the development of this Technical Report is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available at <a href="https://www.iec.ch/members\_experts/refdocs">www.iec.ch/members\_experts/refdocs</a>. The main document types developed by IEC are described in greater detail at <a href="https://www.iec.ch/standardsdev/publications">www.iec.ch/standardsdev/publications</a>.

A list of all parts in the IEC 62878 series, published under the general title *Device embedding* assembly technology, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under webstore.iec.ch in the data related to the specific document. At this date, the document will be

- reconfirmed,

- withdrawn,

- · replaced by a revised edition, or

- amended.

IMPORTANT – The "colour inside" logo on the cover page of this document indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

# PREVIEW (standards.iteh.ai)

IEC TR 62878-2-9:2022 https://standards.iteh.ai/catalog/standards/sist/882cdbb5-fbf0-48fe-aecf-e6f2aed32618/iec-tr-62878-2-9-2022

#### INTRODUCTION

The term and definition of JISSO Level had been developed originally at the sixth Jisso International Council (JIC) meeting held in Herndon VA, USA in May 2005 among the experts from North America, Europe and Japan on assembly/packaging technology involving semiconductors, passive devices, PWB, their materials and board design.

The term "JISSO" stands for "total solution for interconnecting, assembling, packaging, mounting and integrating system design for system integration".

JIC started at the Headquarter of IPC in Chicago, USA in 2000 according to the agreement made by TC 91 (Electronics assembly technology, Chairman: the late Mr. Dieter Bergman) and IEC SC 47D (Semiconductor device packaging, Chairman: the late Mr. Martin G. Freedman) based on the proposal made by JNC members of TC 91 and SC 47D (Mr. Katsumi Yamamoto and Mr. Hisao Kasuga) at the 63th IEC General meeting in Kyoto in 1999.

Restructuring on JIC activities was discussed at the 14<sup>th</sup> JIC meeting held in Seoul, S. Korea in April 2013 with the following conclusion:

The purpose of this council is to provide a platform to enable a strategic collaboration among stakeholders that create benefits along the value chain of interconnecting, assembling, packaging, mounting, integrating system design, and focused technologies by increasing global awareness.

To accomplish these objectives, members will collaborate to evaluate technology and market trends, to identify and address gaps not publicly recognized, and to provide inputs or potential solutions to the electronic industry, academia, standardization bodies and regulatory institutions.

These activities will be undertaken in a spirit of responsibility to the worldwide electronic industry.  $\underline{\text{IEC TR } 62878\text{-}2\text{-}9\text{:}2022}$

https://standards.iteh.ai/catalog/standards/sist/882cdbb5-fbf0-48fe-aecf-e6f2aed32618/iec-tr-62878-2-9-2022

#### DEVICE EMBEDDING ASSEMBLY TECHNOLOGY -

## Part 2-9: Guidelines – Concept of JISSO Level in the electronic assembly technology industries

### 1 Scope

The purpose of this Technical Report is to comprise the long-term discussion among Jisso International Council (JIC) members during 1999 and 2005, when the interim agreement among all JIC members about the "concept of Jisso" as well as the "Jisso product level" for the common understanding on IEC TC 91 (electronic assembly technology) activities was reached.

Further discussion on "Jisso Product Level" could be needed among the current JIC members to finalize it in the near future based on this technical report.

#### 2 Normative references

There are no normative references in this document. DARD

#### 3 Terms

**PREVIEW**

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses: IEC TR 62878-2-9:2022

- https://standards.iteh.ai/catalog/standards/sist/882cdbb5-IEC Electropedia: available at http://www.electropedia.org/ thttp://www.electropedia.org/ 1510-481e-aeci-eoi/2aed32618/1ec-tr-628/8-2-9-2022

- ISO Online browsing platform: available at http://www.iso.org/obp

#### 3.1 Jisso JISSO

total solution for interconnecting, assembling, packaging, mounting and integrating system design for system integration

#### 4 Historical Concept of Jisso (JISSO)

#### 4.1 Some examples of terms on Jisso/JISSO used in the past

- a) Packaging

- Total technique of interconnecting, assembling, packaging, mounting for electronic system (proposed by Prof. Rao Tummala, GIT/IBM in USA in 1991: similar to the concept of Jisso);

- ii) The process of assembling one or more electronic components into a package (as per IEC 60194:2015<sup>1</sup> terms and definitions of IEC TC 91);

- iii) The process of packing products into transportation container.

NOTE 1 Other terminologies:

"Electronic packaging" is at least recommended when this word is being used alone.

Withdrawn (cancelled and replaced by IEC 60194-1:2021 and IEC 60194-2:2017)

"Assembling" is a common term used for various levels like electronic package (of semiconductor device), electronic module, electronic unit and electronic set

#### b) System integration

defined by METI and ASET(see Note 2) in 1996 in Japan

#### NOTE 2

METI: Ministry of Economy, Trade and Industry (Japan).

ASET: Association of Super Advanced Electronics Technologies (Japan).

c) System design and integration

proposed by Professor Nakata (Osaka University) in 1996 in Japan

d) Jisso/JISSO

Total solution for interconnecting, assembling, packaging, mounting and integrating system design for system integration as shown in Figure 1.

Figure 1 - Concept of Jisso/JISSO

This concept had been introduced in public by "Electronic Interconnections No. 10 – The Jisso International Council" in May  $30^{th}$ , 2006.

"The Jisso International Council (JIC), comprised of Asian, European and North American Jisso councils and supported by all major electronics industry trade and technology associations, including: IPC, JEITA, iNEMI, JEDEC, EIPC, JPCA and others, has just finished its 7th annual meeting. The major council co-chaired by Hisao Kasuga of NEC representing the Jisso Japan Council, Bernd Roemer of Infineon, representing the Jisso European Council and Denny Fritz of McDermid representing the Jisso North America Council. The meeting was in Berlin, Germany at IZM – Fraunhofer Institute for Reliability and Microintegration. Now, after seven years of quiet behind the scenes effort, this group of highly dedicated engineers and managers, representing electronic companies from around the world and who make up the JIC, is poised to pay some important dividends to the electronics industry."

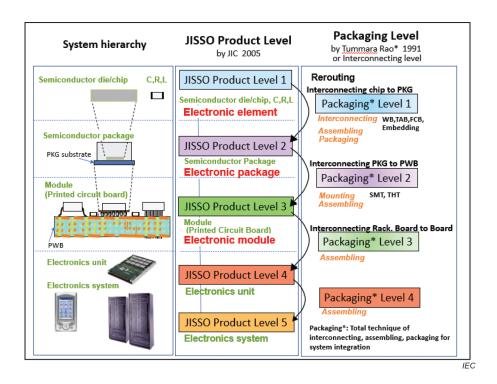

#### 4.2 JISSO level versus Packaging Level (Interconnecting Level)

#### 4.2.1 JISSO Level (typical)

The Jisso Level is proposed by Mr. Dieter Bergman, the former chairman of TC 91, IPC director as follows:

- a) JISSO Level is defined by Jisso product type from a supplier to a user;

- b) JISSO considers two different aspects; Functional and Physical states;

- c) JISSO Product Levels are divided by Physical states;

- d) JISSO Product Level is defined by Physical state before Jisso process;

- e) JISSO Interface Level is defined by a type of Jisso process, such as Interconnecting process which is called "Packaging process", or better, "Assembly process".

NOTE The concept described in 4.2.2 created confusion when used as Packaging Levels other than "Level 1". It became inconsistent to terminology used in general in assembly technology. In current understanding, the term "packaging" is used to describe those component manufacturing processes, which assemble functional elements into a package to form the final component. Level 2 and above cannot be called "packaging".

#### 4.2.2 Packaging Level

Packaging Level proposed by Professor Rao Tummala, GIT/IBM in USA in 1991 represent Interconnecting Level between the lower level and the next higher level of electronic product, such as a chip, a package, a PWB (a circuit board), Rack, board, unit, set, as shown in Figure 2.

- a) "Packaging Level 1" is shown as interconnecting of chip to package like "Electronic element" (JISSO Product Level 1) to "Electronic package (JISSO Product Level 2)" using WB, TAB, FCB including Embedding technology. In other general words, "Interconnecting", "Assembling", "Packaging" and so on.

- b) "Packaging Level 2" is shown as interconnecting of package to PWB like "Electronic package (JISSO Product Level 2)" to PWB of a circuit board of a "Electronic module (Jisso product level 3)" or a circuit board of other upper level of electronic product. In other general words, "Mounting" like SMT or THT, "Assembling", "Soldering" and so on.

- c) "Packaging Level 3" is shown as interconnecting of Rack/board to board like "Electronic module (JISSO Product Level 3) to "Electronics unit (JISSO Product Level 4)". In another general words, "Assembling".

Figure 2 shows the relation between a typical JISSO Level (JISSO Product Level) versus Packaging Level (Interconnecting Level).

Figure 2 - Relation between JISSO Level versus Packaging Level

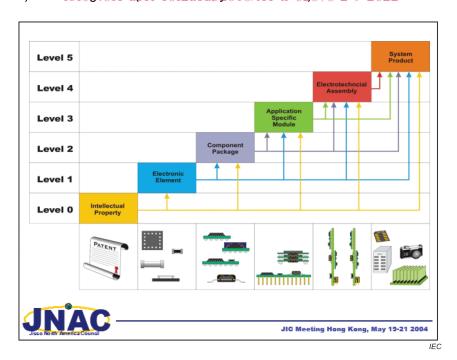

## 5 Concept of typical terms and description on JISSO Level

#### 5.1 JISSO/Jisso

(standards.iteh.ai)

Integrated system design and manufacturing related to implementing technology solutions among user and supplier covering the technologies of interconnection, assembling, packaging, mounting and board design as shown in Figure 3 (introduced by JISSO North America Council [JNAC] in 2004) and in Figure 4 (introduced by JUC in 2005): 78-2-9-2022

Figure 3 – JISSO Level Concept (1) preliminarily introduced by JNAC in 2004