Edition 1.0 2022-02

# **INTERNATIONAL STANDARD**

## NORME **INTERNATIONALE**

Dynamic on-resistance test method guidelines for GaN HEMT based power conversion devices **R**H conversion devices

Lignes directrices pour les méthodes d'essai de résistance dynamique à l'état passant des dispositifs de conversion de puissance fondés sur les HEMT en GaN IEC 63373:2022

https://standards.iteh.ai/catalog/standards/sist/290730b4-1c36-44d1-a0a1-c769dcc6dddd/iec-63373-2022

## THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2022 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

**IEC** Secretariat 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Tel.: +41 22 919 02 11 info@iec.ch www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigendum or an amendment might have been published.

#### IEC publications search - webstore.iec.ch/advsearchform

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee, ...). It also gives information on projects, replaced and withdrawn publications.

IEC Just Published - webstore.iec.ch/justpublished Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and once a month by email.

#### IEC Products & Services Portal - products.iec.ch

Discover our powerful search engine and read freely all the publications previews. With a subscription you will always have access to up to date content tailored to your needs.

#### Electropedia - www.electropedia.org

The world's leading online dictionary on electrotechnology, containing more than 22 300 terminological entries in English and French, with equivalent terms in 19 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

### IEC Customer Service Centre - webstore.iec.ch/cscEC 63

If you wish to give us your feedback on this publication of alog/standards/sist/290730b4need further assistance, please contact the Customer Service c36-44d1-a0a1-c769dcc6dddd/iec-63373-2022 Centre: sales@iec.ch.

#### A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

#### A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l'édition la plus récente, un corrigendum ou amendement peut avoir été publié.

#### Recherche de publications IEC -

### webstore.iec.ch/advsearchform

La recherche avancée permet de trouver des publications IEC en utilisant différents critères (numéro de référence, texte, comité d'études, ...). Elle donne aussi des informations sur les projets et les publications remplacées ou retirées.

#### IEC Just Published - webstore.iec.ch/justpublished

Restez informé sur les nouvelles publications IEC. Just Published détaille les nouvelles publications parues. Disponible en ligne et une fois par mois par email.

#### Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions contactez-nous: sales@iec.ch.

#### IEC Products & Services Portal - products.iec.ch

Découvrez notre puissant moteur de recherche et consultez gratuitement tous les aperçus des publications. Avec un abonnement, vous aurez toujours accès à un contenu à jour adapté à vos besoins.

#### Electropedia - www.electropedia.org

Le premier dictionnaire d'électrotechnologie en ligne au monde, avec plus de 22 300 articles terminologiques en anglais et en français, ainsi que les termes équivalents dans 19 langues additionnelles. Egalement appelé Vocabulaire Electrotechnique International (IEV) en ligne.

Edition 1.0 2022-02

## INTERNATIONAL STANDARD

## NORME INTERNATIONALE

## iTeh STANDARD

Dynamic on-resistance test method guidelines for GaN HEMT based power conversion devices

Lignes directrices pour les méthodes d'essai de résistance dynamique à l'état passant des dispositifs de conversion de puissance fondés sur les HEMT en GaN

https://standards.iteh.ai/catalog/standards/sist/290730b4-1c36-44d1-a0a1-c769dcc6dddd/iec-63373-2022

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

ICS 31.080.99

ISBN 978-2-8322-1076-6

Warning! Make sure that you obtained this publication from an authorized distributor. Attention! Veuillez vous assurer que vous avez obtenu cette publication via un distributeur agréé.

Registered trademark of the International Electrotechnical Commission Marque déposée de la Commission Electrotechnique Internationale

## CONTENTS

| F        | OREWO                                                                               | )RD                                                                                                                                                           | 3    |  |  |  |

|----------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| IN       | TRODI                                                                               | JCTION                                                                                                                                                        | 5    |  |  |  |

| 1        | Scop                                                                                | pe                                                                                                                                                            | 6    |  |  |  |

| 2        | Norr                                                                                | native references                                                                                                                                             | 6    |  |  |  |

| 3        | Tern                                                                                | ns, definitions, symbols and abbreviated terms                                                                                                                | 6    |  |  |  |

|          | 3.1                                                                                 | Terms and definitions                                                                                                                                         | 6    |  |  |  |

|          | 3.2                                                                                 | Symbols and abbreviated terms                                                                                                                                 | 6    |  |  |  |

| 4        | Test                                                                                | circuits and waveforms                                                                                                                                        | 7    |  |  |  |

|          | 4.1                                                                                 | General                                                                                                                                                       | 7    |  |  |  |

|          | 4.2                                                                                 | Inductive and resistive switching methods                                                                                                                     | 7    |  |  |  |

|          | 4.3                                                                                 | Pulsed current-voltage (I-V) method                                                                                                                           | .10  |  |  |  |

| 5        | Req                                                                                 | uirements                                                                                                                                                     | .12  |  |  |  |

| Bi       | bliogra                                                                             | phy                                                                                                                                                           | .14  |  |  |  |

|          |                                                                                     |                                                                                                                                                               |      |  |  |  |

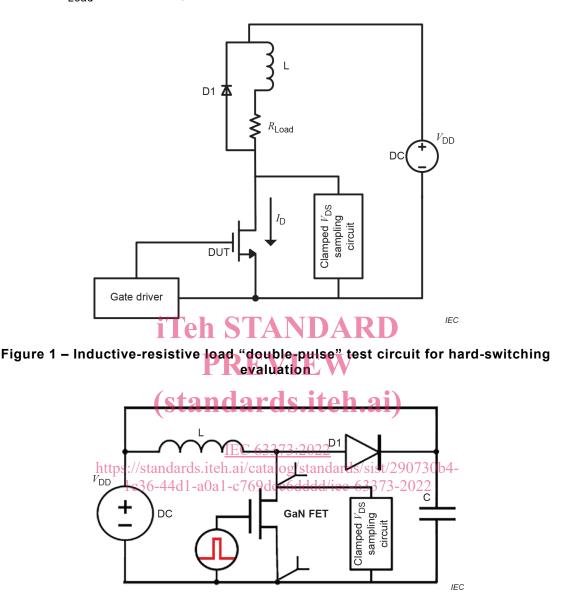

|          |                                                                                     | <ul> <li>Inductive-resistive load "double-pulse" test circuit for hard-switching</li> </ul>                                                                   | 8    |  |  |  |

| Fi<br>si | gure 2<br>milarity                                                                  | <ul> <li>Depiction of the hard-switching "double-pulse" test circuit (showing its<br/>to a boost converter)</li> </ul>                                        | 8    |  |  |  |

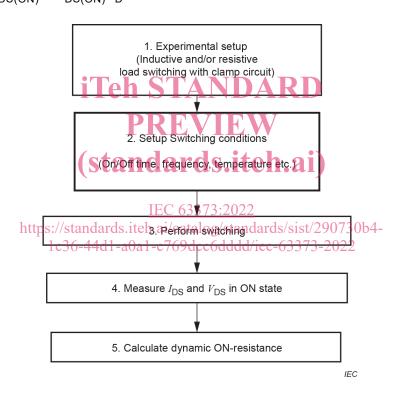

| Fi<br>or | gure 3<br>n-resista                                                                 | <ul> <li>Simplified flowchart for inductive and/or resistive switching based dynamic ance test</li> </ul>                                                     |      |  |  |  |

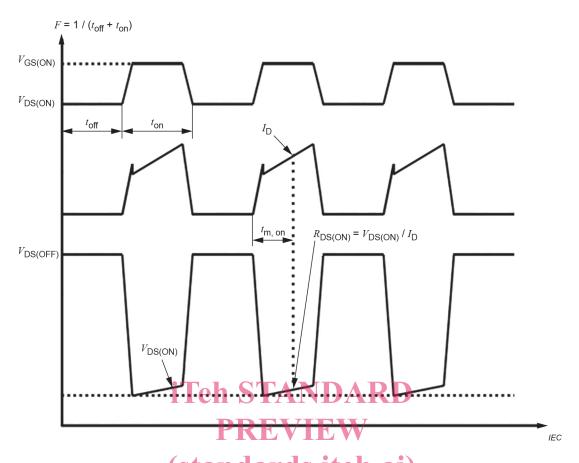

| Fi       | gure 4                                                                              | <ul> <li>Representative continuous-pulse hard-switching waveforms for measuring<br/>on-resistance using the test circuits in Figure 1 and Figure 2</li> </ul> | . 10 |  |  |  |

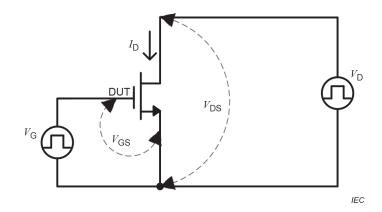

| ar       | nd drain                                                                            | <ul> <li>Example test circuit for soft-switching on-resistance measurement (the gate<br/>terminals are pulsed with independent voltage signals)</li> </ul>    | . 10 |  |  |  |

| Fi       | Figure 6 – Simplified flowchart for soft switching based dynamic on-resistance test |                                                                                                                                                               |      |  |  |  |

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

## DYNAMIC ON-RESISTANCE TEST METHOD GUIDELINES FOR GaN HEMT BASED POWER CONVERSION DEVICES

### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user. In the sense of the sense

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance/upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

IEC 63373 has been prepared by IEC technical committee 47: Semiconductor devices. It is an International Standard.

This standard is based upon JEP173 [1].<sup>1</sup> It is used with permission of the copyright holder, JEDEC Solid State Technology Association.

The text of this International Standard is based on the following documents:

| Draft       | Report on voting |

|-------------|------------------|

| 47/2690/CDV | 47/2735/RVC      |

Full information on the voting for its approval can be found in the report on voting indicated in the above table.

The language used for the development of this International Standard is English.

<sup>&</sup>lt;sup>1</sup> Numbers in square brackets refer to the Bibliography.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available at www.iec.ch/members\_experts/refdocs. The main document types developed by IEC are described in greater detail at www.iec.ch/standardsdev/publications.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under webstore.iec.ch in the data related to the specific document. At this date, the document will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

IMPORTANT – The "colour inside" logo on the cover page of this document indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

## iTeh STANDARD PREVIEW (standards.iteh.ai)

IEC 63373:2022 https://standards.iteh.ai/catalog/standards/sist/290730b4-1c36-44d1-a0a1-c769dcc6dddd/iec-63373-2022

### INTRODUCTION

This document is intended for use in the GaN power semiconductor and related power electronic industries, and provides guidelines for measuring the dynamic ON-resistance of GaN power devices.

Gallium Nitride (GaN) lateral power High Electron Mobility Transistor (HEMT) conducts through a two-dimensional electron gas (2DEG) in ON-state operation. Due to the various stress conditions that the device encounters during power electronic switching applications, some charge could get trapped in specific regions of the transistor structure. The trapped electrons cause an increased ON-resistance when operated in a switching environment. This phenomenon is known as current collapse and the ON-resistance at switching operation is called dynamic ON-resistance in order to distinguish from DC ON-resistance. Increased dynamic ON-resistance translates to higher power loss, thereby reducing overall system efficiency. Not verifying the dynamic ON-resistance characteristic can put GaN device reliability at risk [2].

The test methods provided in this document can be used as a guideline for measuring dynamic ON-resistance of GaN power device, focused on lateral HEMT technologies. These three test methods can be applied for datasheet, process control, technology development, final tests and other usage. Parasitic effects impact high precision measurements and wafer level tests can minimize parasitic effects. Additionally, self-heating can impact the package level tests depending upon the package thermal characteristics.

## PREVIEW (standards.iteh.ai)

IEC 63373:2022 https://standards.iteh.ai/catalog/standards/sist/290730b4-1c36-44d1-a0a1-c769dcc6dddd/iec-63373-2022

## DYNAMIC ON-RESISTANCE TEST METHOD GUIDELINES FOR GaN HEMT BASED POWER CONVERSION DEVICES

### 1 Scope

In general, dynamic ON-resistance testing is a measure of charge trapping phenomena in GaN power transistors. This publication provides guidelines for testing dynamic ON-resistance of GaN lateral power transistor solutions. The test methods can be applied to the following:

- a) GaN enhancement and depletion-mode discrete power devices [3];

- b) GaN integrated power solutions;

- c) the above in wafer and package levels.

The prescribed test methods can be used for device characterization, production testing, reliability evaluations and application assessments of GaN power conversion devices. This document is not intended to cover the underlying mechanisms of dynamic ON-resistance and its symbolic representation for product specifications.

## 2 Normative references Teh STANDARD

There are no normative references in this document.

## 3 Terms, definitions, symbols and abbreviated terms

### 3.1 Terms and definitions

## IEC 63373:2022

No terms and definitions/are listed in this document tandards/sist/290730b4-1c36-44d1-a0a1-c769dcc6dddd/iec-63373-2022

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at http://www.electropedia.org/

- ISO Online browsing platform: available at http://www.iso.org/obp

### 3.2 Symbols and abbreviated terms

| Symbol or abbreviation | Name or term                                  |

|------------------------|-----------------------------------------------|

| DUT                    | Device Under Test                             |

| V <sub>DD</sub>        | Supply voltage                                |

| V <sub>DS</sub>        | Drain to Source Voltage of DUT                |

| V <sub>GS</sub>        | Gate to Source Voltage of DUT                 |

| D1                     | Free-wheeling diode                           |

| L                      | Inductance                                    |

| R                      | Resistance                                    |

| С                      | Capacitance                                   |

| ID                     | Drain current of DUT in ON-state              |

| V <sub>DS(ON)</sub>    | Drain to Source Voltage of DUT in ON-state    |

| R <sub>DS(ON)</sub>    | Drain to Source Resistance of DUT in ON-state |

| Symbol or abbreviation | Name or term                                                                             |

|------------------------|------------------------------------------------------------------------------------------|

| $V_{\text{DS(OFF)}}$   | Drain to source voltage of DUT in OFF-state                                              |

| $V_{\rm GS(ON)}$       | Gate to source voltage of DUT in ON-state                                                |

| V <sub>gs(off)</sub>   | Gate to source voltage of DUT in OFF-state                                               |

| t <sub>off</sub>       | OFF-state pulse width                                                                    |

| t <sub>on</sub>        | ON-state pulse width                                                                     |

| t <sub>m,on</sub>      | measurement timing in ON-pulse                                                           |

| t <sub>dn</sub>        | Soft-switching delay time between the OFF and ON pulse or vice-versa, with n = 1 or 2 $$ |

| f                      | Frequency                                                                                |

| N                      | Number of pulses                                                                         |

| T <sub>C</sub>         | Case temperature                                                                         |

| P <sub>Peak</sub>      | Instantaneous peak power, applicable for only hard switching                             |

| E <sub>Pulse</sub>     | Energy dissipated per pulse, applicable for only hard switching                          |

## 4 Test circuits and waveforms STANDARD PREVIEW

#### 4.1 General

GaN power transistors typically are being targeted for both hard and soft-switching topologies for power conversion applications and ards. Iten.al

Hard switching conditions refer to the overlap of the voltage and current waveforms when the power device switches either from ON-to-OFF or OFF-to-ON states. Typical hard-switching topologies include totem-pole Power Factor Correction (PFC) boost converters, buck converters, motor control inverter and single ended fly-back circuits iec-63373-2022

Soft switching conditions refer to conditions where there is no or minimal overlap of the voltage and current waveforms when the GaN power device switches between the ON- and OFF-states. Typical soft-switching topologies include Zero Voltage Switching (ZVS) converters, LLC converters, Active Clamp Fly-back (ACF), etc.

Resistive load switching is another type that is not typically seen in the power electronic applications whose overlap of voltage and current waveforms fall in between the hard and soft switching types. However, the easier implementation of this switching type makes it attractive for the device level characterization and testing purposes.

As described above, current-voltage loci are the crux that determines the switching type. The loci of above three switching types are explained with great detail in here [4]. The following 4.2 and 4.3 cover the dynamic ON-resistance measurement methods for these three switching types.

Minimizing parasitic effects when performing high precision measurements is recommended. Wafer level tests can be used to minimize parasitic effects when performing high precision measurements. For package level tests, the impact of package thermal characteristics should be considered so as to minimize any device under test (DUT) self-heating implications.

#### Inductive and resistive switching methods 4.2

A hard-switching inductive and resistive loaded test vehicle that is analogous to what is generally termed the "double-pulse" tester in power electronic applications [2] is shown in Figure 1. Another depiction of the double-pulse tester is shown in Figure 2, which illustrates that the double-pulse tester is equivalent to a boost converter with the input tied to the output [5]; note that  $R_{Load} = 0$  in this depiction.

## Figure 2 – Depiction of the hard-switching "double-pulse" test circuit (showing its similarity to a boost converter)

When a power transistor switches at high voltages, measuring the drain-to-source ON-state voltage with a passive probe in combination with an oscilloscope can be quite challenging, as the oscilloscope's dynamic-range precision may not be adequate. As an example, consider a device with an ON-state voltage of 0,5 V at 1 A of drain current switching from 400 V in the OFF-state. An 8-bit oscilloscope configured to measure the 400 V OFF-state voltage will have a resolution of 1,562 5 V (=  $400/2^8$ ), which is not sufficient to measure the 0,5 V ON-state voltage. The measurable voltage has an error of more than 3 times the actual voltage in this example and this further increase to 30 times to detect a 10 % dynamic ON-state voltage drift. To circumvent such problems, a circuit may be employed to clamp the high OFF-state voltage on a low-voltage measurement probe without compromising the ON-state voltage.

Since the clamped sampling circuit reduces the voltage swing quite significantly on the measurement probe, the dynamic ON-state voltage of the power transistor can be effectively measured, from which its dynamic ON-resistance is calculated using Ohm's law. Some examples of voltage clamp sampling circuits are reported in [6] and [7].

It is to be noted that if  $R_{Load} = 0$  in Figure 1 (which makes the circuits of Figure 1 and Figure 2 identical), the circuit is nothing but a standard power electronics double-pulse or boost test circuit. The hard-switching circuits presented in Figure 1 and Figure 2 provide the flexibility of running tests either in single-pulse, double-pulse or continuous-pulse modes. They provide high impedance on the drain, which lowers  $V_{\text{DS}}$  without the need for an additional synchronized tester resource. A high impedance may also be achieved by setting L = 0 and using a highvalue resistor making this a pure resistive switching. The single and double-pulse test modes are often advantageous in production environments where fast switching characterization is needed, whereas the continuous-pulse test mode is beneficial for longer-term device characterization and reliability evaluation. The flow chart for inductive and/or resistive switching load-based measurement is presented in Figure 3, and Figure 4 shows the representative hardswitching waveforms of a GaN power transistor in the Figure 1 and Figure 2 test circuits when subjected to continuous gate pulses. In a pure resistive switching load test circuit, the DUT current in ON-state stays constant unlike the inductive load circuit where the current increases linearly with time. A high-performance clamp circuit design may be required to measure the drain-to-source dynamic ON-resistance in <1 µs after the device transitions from the OFF-state to the ON-state. The  $R_{DS(ON)}$  is evaluated dynamically during the period when the transistor gate is ON as  $R_{\text{DS}(\text{ON})} = V_{\text{DS}(\text{ON})}/I_{\text{D}}$ .

Figure 3 – Simplified flowchart for inductive and/or resistive switching based dynamic on-resistance test

## Figure 4 – Representative continuous pulse hard switching waveforms for measuring dynamic on-resistance using the test circuits in Figure 1 and Figure 2

### 4.3 Pulsed current-voltage (I-V) method https://standards.iteh.ai/catalog/standards/sist/290730b4-

The pulsed I-V technique is 4 analogous cto soft switching, (which is 2007 Store in GaN RF

electronics. This method involves pulsing the gate and drain voltage signals independently, and hence is branded as a classic "double pulse" technique in the RF world, thus potentially leading to confusion since this term is used in the power electronics world to refer to a hard-switching test, as discussed above. Using this approach, a few manufacturers have developed systems to fulfil power electronic requirements [8]. Figure 5 and Figure 6 provide simplified test setup and test flow respectively for soft switching.

Figure 5 – Example test circuit for soft-switching on-resistance measurement (the gate and drain terminals are pulsed with independent voltage signals)