# INTERNATIONAL STANDARD

# IEC 60191-6-12

First edition 2002-06

Mechanical standardization of semiconductor devices – Part 6-12:

General rules for the preparation of outline drawings of surface mounted semiconductor device packages – Design guide for fine-pitch land grid array (FLGA) – Rectangular type

Normalisation mécanique des dispositifs à semiconducteurs -

Partie 6-12:

Règles générales pour la préparation des dessins d'encombrement des dispositifs à semiconducteurs pour montage en surface — 2 9 dea-0a9215511956 lec-60191-6-1 Guide de conception pour les boîtiers FLGA de type rectangulaire

### **Publication numbering**

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

#### **Consolidated editions**

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

### Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC catalogue of publications (see below) in addition to new editions, amendments and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

- IEC Web Site (<u>www.iec.ch</u>)

- Catalogue of IEC publications

The on-line catalogue on the IEC web site (<a href="www.iec.ch/catig-e.mtm">www.iec.ch/catig-e.mtm</a>) enables you to search by a variety of criteria including text searches, technical committees and date of publication. On-line information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

IEC Just Published

This summary of recently issued publications (<a href="www.iec.ch/JP.htm">www.iec.ch/JP.htm</a>) is also available by email. Please contact the Customer Service Centre (see below) for further information.

Customer Service Centre

If you have any guestions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email: <u>custserv@ec.ch</u> Tel: +41 22 919 02 11 Fax: +41 22 919 03 00

# INTERNATIONAL STANDARD

# IEC 60191-6-12

First edition 2002-06

Mechanical standardization of semiconductor devices – Part 6-12:

General rules for the preparation of outline drawings of surface mounted semiconductor device packages – Design guide for fine-pitch land grid array (FLGA) – Rectangular type

Normalisation mécanique des dispositifs à semiconducteurs –

Partie 6-12:

Règles génèrales pour la préparation des dessins d'encombrement des dispositifs à semiconducteurs pour montage en surface – 2-9 des -0.9925511956/icc-60191-6-1 Guide de conception pour les boîtiers FLGA de type rectangulaire

© IEC 2002 — Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

PRICE CODE

R

# CONTENTS

| FΟ  | REWORD3                                                                                                   |

|-----|-----------------------------------------------------------------------------------------------------------|

| INT | RODUCTION4                                                                                                |

| 1   | Scope5                                                                                                    |

| -   |                                                                                                           |

| 2   | Normative references5                                                                                     |

| 3   | Definitions5                                                                                              |

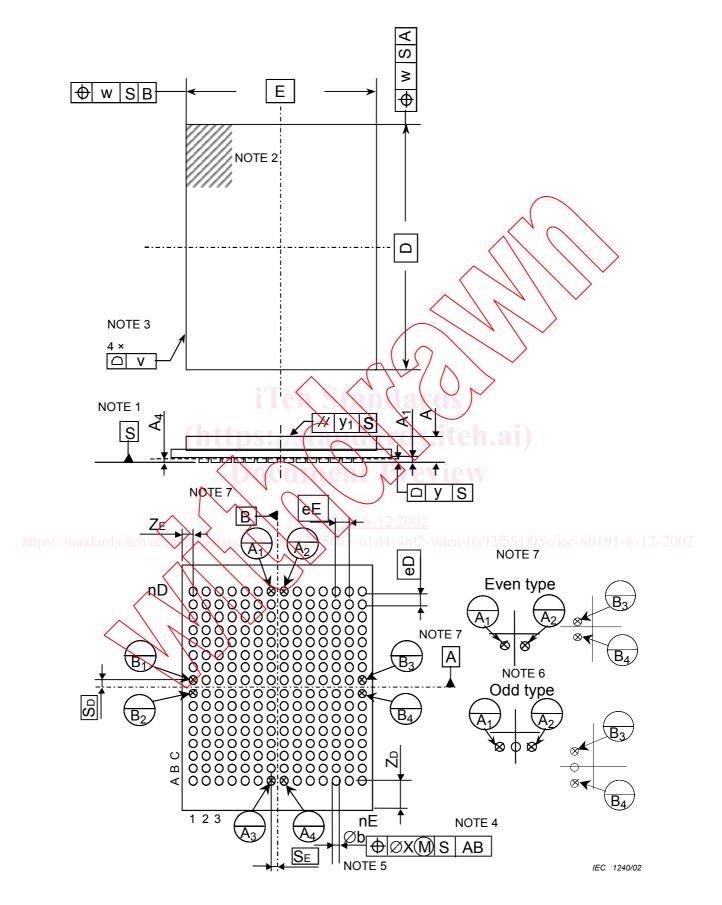

| Fig | ure 1 – Rectangular FLGA packages6                                                                        |

| Fig | ure 2 – Terminal zones                                                                                    |

| Tal | ole 1 – Group 1: Dimensions appropriate to mounting and interchangeability8                               |

|     | ole 2 – Group 2: Dimensions appropriate to mounting and gauging11                                         |

| Tal | ole 3 – Package dimensions                                                                                |

| Tal | ole 4 – D/E, nD/nE, n max. variation – e = 0,80 mm pitch/FLGA flanged type13                              |

| Tal | ole 5 – D/E, nD/nE, n max. variation – e = 0,65 mm pitch FLGA flanged type14                              |

| Tal | ole 6 – D/E, nD/nE, n max. variation – e = 0,50 mm pitch FLGA flanged type15                              |

| Tal | ole 7 – D/E, nD/nE, n max. variation – e = 0,40 mm pitch FLGA flanged type16                              |

| Tal | ole 8 – D/E, nD/nE, n max. variation – e = 0.80 mm pitch FLGA real chip size type17                       |

| Tal | ole 9 – D/E, nD/nE, n max. variation – e = 0,65 mm pitch FLGA real chip size type18                       |

| Tal | ole 10 – D/E, nD/nE, n max variation – e = 0.50 mm pitch FLGA real chip size type19                       |

| Tal | ole 11 – D/E, nD/nE, n max variation – e ≠ 0,40 mm pitch FLGA real chip size type20                       |

|     | and and a state of the attended to 12 /47 5 /2 61 d.4 Abril 0 day 0 a 0.255 1405 a line 60 1 0 1 6 12 200 |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### MECHANICAL STANDARDIZATION OF SEMICONDUCTOR DEVICES -

Part 6-12: General rules for the preparation of outline drawings of surface mounted semiconductor device packages –

Design guide for fine-pitch land grid array (FLGA) –

Rectangular type

#### **FOREWORD**

- 1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested National Committees.

- 3) The documents produced have the form of recommendations for international use and are published in the form of standards, technical specifications, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEC National Committees undertake to apply IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

- 5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with one of its standards.

- 6) Attention is drawn to the cossibility that some of the elements of this International Standard may be the subject of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60191-6-12 has been prepared by subcommittee 47D: Mechanical standardization of semiconductor devices, of IEC technical committee 47: Semiconductor devices.

The text of this standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 47D/493/FDIS | 47D/507/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 3.

A bilingual version of this publication may be issued at a later date.

The committee has decided that the contents of this publication will remain unchanged until 2004. At this date, the publication will be

- reconfirmed;

- · withdrawn;

- replaced by a revised edition, or

- amended.

# INTRODUCTION

The demand for area array style packages exists because of the multi-functions and high performance of electrical equipment. The objective of this design guide is to standardize outlines and to get interchangeability of FLGA rectangular type packages. The terminal pitch and package outlines of these fine-pitch array packages are smaller than those of LGA packages.

### MECHANICAL STANDARDIZATION OF SEMICONDUCTOR DEVICES -

# Part 6-12: General rules for the preparation of outline drawings of surface mounted semiconductor device packages – Design guide for fine-pitch land grid array (FLGA) – Rectangular type

# 1 Scope

This part of IEC 60191 provides common outline drawings and dimensions for all types of structures and composed materials of fine-pitch land grid array (hereinafter called FLGA) whose terminal pitch is less than, or equal to, 0,80 mm and whose package body outline is rectangular.

#### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60191 (all parts), Mechanical standardization of semiconductor devices

# 3 Definitions

For the purposes of this part of IEC 60191, the following definitions, as well as those given in the other parts of this series, apply

# 3.1

#### flanged type

type whose package body size (body length and width) consists of its own flange composed around the encapsulation or lid

#### 3.2

#### type of real chip size

type whose package body size (body length and width) consists of an encapsulation around the real ship only

### 3.3

#### **FLGA**

packages with metal lands or metal bumps of which the terminal height is less than, or equal to,  $100~\mu m$ , and whose terminal pitch is less than, or equal to, 0.80~mm, positioned in an array on the base plane of the package as external terminals

This package structure makes it possible to surface-mount the packages to the printed circuit board.

#### 3.4

#### material designation

FLGA packages are classified according to the following two material designations:

#### 3.4.1

#### plastic type (P-FLGA)

plastic-type classification is assigned to packages which consist of resin substrate as interposer material (for example, glass-epoxy, poly-imid)

#### 3.4.2

#### ceramic type (C-FLGA)

ceramic-type classification is assigned to packages which consist of ceramic substrate as interposer material

Figure 1 - Rectangular FLGA packages

- NOTE 1 Indicates seating plane. Seating plane is defined by the plane that the carrier contacts to the mount surface.

- NOTE 2 Indicates positional tolerance of the index mark.

- NOTE 3 Bilateral tolerance zone is applied to four sides of the package body.

- NOTE 4 The positional tolerances are applied to all terminals.

- NOTE 5 Terminal diameter is the maximum terminal profile when the package is projected vertically from the seating plane.

- NOTE 6 SD and SE are stipulated the position of closest terminal with respect to datum lines A and B.

- NOTE 7 Datum A and B are the axes defined by the centres of the opposite package sides of the ball. The definition of the centre applies to "Odd type" and "Even type".

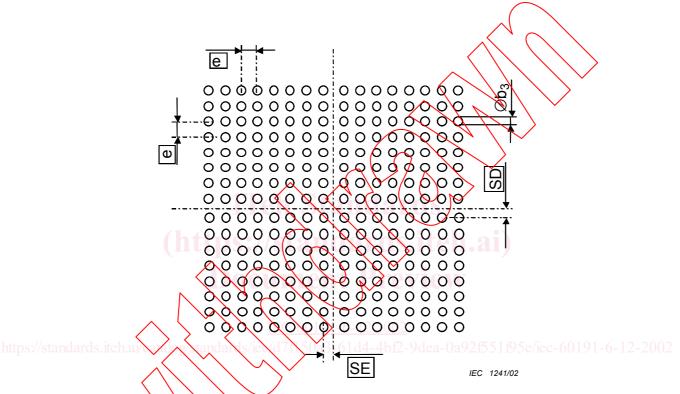

NOTE As foot circuit pattern design reference, the zone in which the terminals can be positioned is shown in this figure.

Figure 2 - Terminal zones

Table 1 – Group 1: Dimensions appropriate to mounting and interchangeability

Dimensions in millimetres

| Name                    | Reference symbol                                                                                                                | Stipulations                                                                                                                                                                                                                      | Recommended value      | Supplement       |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|

| Nominal E × D dimension | E×D                                                                                                                             | Flanged type                                                                                                                                                                                                                      | _                      | E < D            |

|                         | The combination of one digit below decimal point of package width E and package length D is considered as the nominal dimension |                                                                                                                                                                                                                                   | is not defined         |                  |

|                         |                                                                                                                                 | Type of real chip size                                                                                                                                                                                                            |                        |                  |

|                         |                                                                                                                                 | The combination of two digits below decimal point of package width E and package length D is considered as the nominal dimension                                                                                                  |                        |                  |

| Package D               | D                                                                                                                               | 1) Flanged type                                                                                                                                                                                                                   | <u> </u>               |                  |

| length                  |                                                                                                                                 | Package length: Dnom                                                                                                                                                                                                              |                        |                  |

|                         |                                                                                                                                 | D = 1,5, 2,0, 2,5, 3,0, 3,5, 4,0, 4,5, 5,0, 5,5, 6,0, 6,5, 7,0, 7,5, 8,0, 8,5, 9,0, 9,5, 10,0, 10,5, 11,0, 11,5, 12,0, 12,5, 13,0, 13,5, 14,0, 14,5, 15,0, 15,5, 16,0, 16,5, 17,0, 17,5, 18,0, 18,5, 19,0, 19,5, 20,0, 20,5, 21,0 |                        | <b>`</b>         |

|                         | 2) Type of real chip size                                                                                                       | $\searrow$                                                                                                                                                                                                                        | Dimension              |                  |

|                         | Package length: Dnom                                                                                                            | >                                                                                                                                                                                                                                 | range shows<br>nominal |                  |

|                         |                                                                                                                                 | D = From 1,5 to 21,0                                                                                                                                                                                                              |                        | value            |

| Package E               | E                                                                                                                               | 1) Flanged type                                                                                                                                                                                                                   | - • -                  |                  |

| width                   | (n                                                                                                                              | Package width: Enom                                                                                                                                                                                                               |                        |                  |

|                         |                                                                                                                                 | E=1,5,2,0,2,5,3,0,3,5,4,0,4,5,5,0,5,5,0,0,6,5,7,0,7,5,8,0,9,5,9,0,9,5,10,0,10,5,11,0,11,5,12,0,12,5,13,0,13,5,14,0,14,5,15,0,15,5,16,0,16,5,17,0,17,5,18,0,18,5,19,0,19,5,20,0,20,5,21,0                                          |                        |                  |

| ://standards.it         |                                                                                                                                 | 2) Type of real chip size 61d4-4bf2-9dea-0                                                                                                                                                                                        |                        | Dimension 2      |

| // Starraar as.it       |                                                                                                                                 | Rackage width: Enom                                                                                                                                                                                                               |                        | range shows      |

|                         |                                                                                                                                 | E = From 1,5 to 21,0                                                                                                                                                                                                              |                        | nominal<br>value |