# TECHNICAL SPECIFICATION

First edition 2007-02

Logic digital integrated circuits – Specification for I/O interface model for integrated circuit (IMIC version 1.3)

## iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>IEC TS 62404:2007</u> https://standards.iteh.ai/catalog/standards/sist/760b77d6-a078-4f3f-b027f64edc5d7569/iec-ts-62404-2007

Reference number IEC/TS 62404:2007(E)

#### **Publication numbering**

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

#### **Consolidated editions**

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

#### Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC Catalogue of publications (see below) in addition to new editions, amendments and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

- IEC Web Site (<u>www.iec.ch</u>)

- Catalogue of IEC publications

The on-line catalogue on the IEC web site (<u>www.iec.ch/searchpub</u>) enables you to search by a variety of criteria including text searches, technical committees and date of publication. On-line information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

## • IEC Just Published standards.iteh.ai)

This summary of recently issued publications (<u>www.iec.ch/online\_news/justpub</u>) is also available by email. Please contact the Customer Service Centre (see below) for further information EC TS 62404:2007

https://standards.iteh.ai/catalog/standards/sist/760b77d6-a078-4f3f-b027-Customer Service Centrelc5d7569/iec-ts-62404-2007

If you have any questions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email: <u>custserv@iec.ch</u> Tel: +41 22 919 02 11 Fax: +41 22 919 03 00

# TECHNICAL SPECIFICATION

First edition 2007-02

Logic digital integrated circuits – Specification for I/O interface model for integrated circuit (IMIC version 1.3)

## iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>IEC TS 62404:2007</u> https://standards.iteh.ai/catalog/standards/sist/760b77d6-a078-4f3f-b027f64edc5d7569/iec-ts-62404-2007

© IEC 2007 — Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

Commission Electrotechnique Internationale International Electrotechnical Commission Международная Электротехническая Комиссия

For price, see current catalogue

## CONTENTS

| FOREWORD4                                                  |                                                                                             |    |  |  |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------|----|--|--|--|--|

| INT                                                        | NTRODUCTION6                                                                                |    |  |  |  |  |

|                                                            |                                                                                             |    |  |  |  |  |

| 1                                                          | Scope                                                                                       | 7  |  |  |  |  |

| 2                                                          | Normative references                                                                        |    |  |  |  |  |

| 3                                                          | Terms and definitions                                                                       |    |  |  |  |  |

| 4                                                          | Outline                                                                                     |    |  |  |  |  |

| 4                                                          | 4.1 General                                                                                 |    |  |  |  |  |

|                                                            | 4.1 General                                                                                 |    |  |  |  |  |

|                                                            | 4.3 Language for circuits                                                                   |    |  |  |  |  |

|                                                            | 4.4 Device model                                                                            |    |  |  |  |  |

|                                                            | 4.5 Structure of model                                                                      |    |  |  |  |  |

|                                                            | 4.6 Simulation                                                                              |    |  |  |  |  |

|                                                            | 4.7 Relation to IBIS                                                                        | .8 |  |  |  |  |

| 5                                                          | Model structure                                                                             | .9 |  |  |  |  |

| 6                                                          | Detailed model description                                                                  | 14 |  |  |  |  |

|                                                            | 6.1 Description rules                                                                       | 14 |  |  |  |  |

|                                                            | <ul> <li>6.1 Description rules</li> <li>6.2 IC model file</li> </ul>                        | 16 |  |  |  |  |

|                                                            | <ul> <li>6.3 Package model file(standards.iteh.ai)</li> <li>6.4 Module model file</li></ul> | 42 |  |  |  |  |

|                                                            | 6.4 Module model file                                                                       | 49 |  |  |  |  |

| 7                                                          | Levels of models                                                                            | 56 |  |  |  |  |

|                                                            | https://standards.iteh.ai/catalog/standards/sist/760b77d6-a078-4f3f-b027-                   |    |  |  |  |  |

| Anr                                                        | f64edc5d7569/iec-ts-62404-2007<br>nex A (informative) Model delivery flow                   | 58 |  |  |  |  |

| Anr                                                        | nex B (informative) Example of model description                                            | 59 |  |  |  |  |

|                                                            |                                                                                             |    |  |  |  |  |

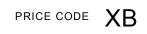

| Fig                                                        | ure 1 – Outline of the model                                                                | .8 |  |  |  |  |

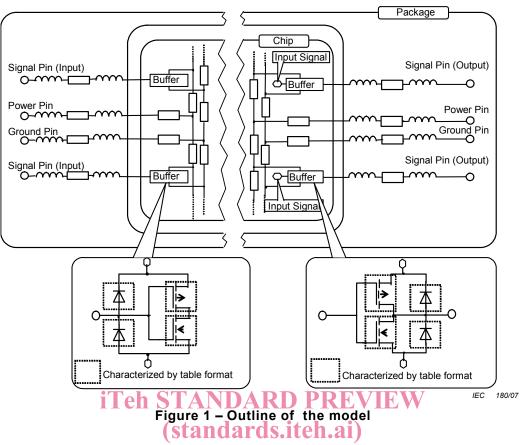

| Fig                                                        | ure 2 – Hierarchy of three models                                                           | .9 |  |  |  |  |

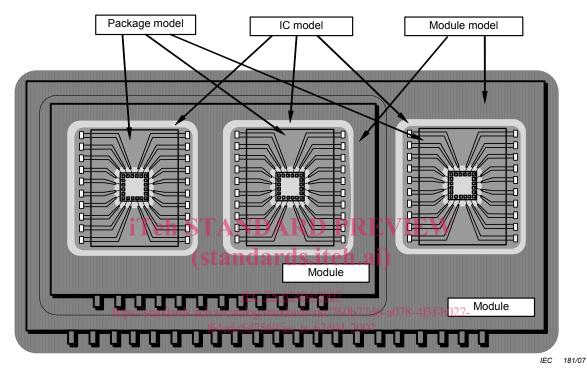

| Fig                                                        | ure 3 – Data structure of an IMIC model file for IC                                         | 11 |  |  |  |  |

| Fig                                                        | ure 4 – Data structure of an IMIC model file for package                                    | 12 |  |  |  |  |

| Figure 5 – Data structure of an IMIC model file for module |                                                                                             |    |  |  |  |  |

| Fia                                                        | Figure 6 – Pad assignment                                                                   |    |  |  |  |  |

| -                                                          | ure 7 – Example of circuit description                                                      |    |  |  |  |  |

| -                                                          | ure 8 – Input stimulus                                                                      |    |  |  |  |  |

| -                                                          | ure 9 – Diode equivalent circuit                                                            |    |  |  |  |  |

|                                                            | ure 10 – Diode characteristics                                                              |    |  |  |  |  |

| -                                                          |                                                                                             |    |  |  |  |  |

| -                                                          | ure 11 – NMOS transistor equivalent circuit                                                 |    |  |  |  |  |

| -                                                          | ure 12 – PMOS transistor equivalent circuit                                                 |    |  |  |  |  |

| -                                                          | ure 13 – Gate channel characteristics of MOS transistor                                     |    |  |  |  |  |

| -                                                          | ure 14 – Characteristics of diode in MOS transistor                                         |    |  |  |  |  |

| -                                                          | ure 15 – NPN transistor equivalent circuit                                                  |    |  |  |  |  |

| Fig                                                        | ure 16 – PNP transistor equivalent circuit                                                  | 35 |  |  |  |  |

| -                                                          | Figure 17 – Static characteristics of bipolar transistor                                    |    |  |  |  |  |

| Fig                                                        | ure 18 – NMOS characteristics on regular grid                                               | 39 |  |  |  |  |

TS 62404 © IEC:2007(E)

| Figure 19 – MOS transistor model with two-terminal model                            | . 39 |

|-------------------------------------------------------------------------------------|------|

| Figure 20 – Relationship between inner terminals and equivalent circuits of package | .46  |

| Figure 21 – Relationship between outer terminals and equivalent circuits of package | .47  |

| Figure 22 – Example of module circuit                                               | . 53 |

| Figure 23 – Example of signal source of module                                      | . 55 |

| Figure A.1 – Delivery flow of model files                                           | . 58 |

| Figure B.1 – IC structure                                                           | . 59 |

| Figure B.2 – Equivalent circuit                                                     | . 59 |

|                                                                                     |      |

| Table 1 – Elements of model structures                                              | . 10 |

| Table 2 – Levels of models                                                          | . 57 |

| Table 3 – Required elements of model for each level                                 | .57  |

## iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>IEC TS 62404:2007</u> https://standards.iteh.ai/catalog/standards/sist/760b77d6-a078-4f3f-b027f64edc5d7569/iec-ts-62404-2007

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

### LOGIC DIGITAL INTEGRATED CIRCUITS – SPECIFICATION FOR I/O INTERFACE MODEL FOR INTEGRATED CIRCUIT (IMIC version 1.3)

#### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- https://standards.itch.ai/catalog/standards/sist/760b77d6-a078-413F-b027 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. In exceptional circumstances, a technical committee may propose the publication of a technical specification when

- the required support cannot be obtained for the publication of an International Standard, despite repeated efforts, or

- the subject is still under technical development or where, for any other reason, there is the future but no immediate possibility of an agreement on an International Standard.

Technical specifications are subject to review within three years of publication to decide whether they can be transformed into International Standards.

IEC 62404, which is a technical specification, has been prepared by subcommittee 47A: Integrated circuits, of IEC technical committee 47: Semiconductor devices.

The text of this technical specification is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 47A/746/DTS   | 47A/751/RVC      |

Full information on the voting for the approval of this technical specification can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A bilingual version of this publication may be issued at a later date.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- transformed into an International standard,

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

## iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>IEC TS 62404:2007</u> https://standards.iteh.ai/catalog/standards/sist/760b77d6-a078-4f3f-b027f64edc5d7569/iec-ts-62404-2007

### INTRODUCTION

With an increase in speed of electronic systems, it becomes necessary to accurately predict electrical performance including noise in electronic systems with integrated circuits.

Simulators have been used for this purpose. Simulators need accurate models for describing electrical properties of integrated circuits. Semiconductor manufacturers and/or suppliers are required by their users to prepare device models for various simulation tools, some of which are not compatible with SPICE. In addition, since SPICE models contain proprietary process parameters, a non-disclosure agreement is typically required to obtain these from the vendor.

IBIS (I/O Buffer Interface Specification) has been proposed as a model for integrated circuits, which, approved as IEC 62014-1, has the following features:

- since electrical properties of I/O buffers are described in table format, disclosure of proprietary information such as process parameters is drastically reduced;

- it is easy to get IBIS models that are supported by many simulation tools;

- a public domain tool can convert SPICE models into IBIS models.

However, IBIS models seem to have the following problems:

- the modeling of power and ground currents is insufficient for accurate power and ground bounce analysis;

- since an IBIS model has only the final stage at output and input, it is difficult to model the

effect of loading on circuit boards on output and input waveforms. The fixed model taken

by IBIS has little flexibility for describing other circuitry.

- in order to simulate EMI with accuracy, more information such as material constant and three-dimensional structures is needed. <u>TS 62404:2007</u> https://standards.iteh.ai/catalog/standards/sist/760b77d6-a078-4f3f-b027-

f64edc5d7569/iec-ts-62404-2007

### LOGIC DIGITAL INTEGRATED CIRCUITS – SPECIFICATION FOR I/O INTERFACE MODEL FOR INTEGRATED CIRCUIT (IMIC version 1.3)

#### 1 Scope

The following items are considered to standardize the electrical modeling of input signals, output signals, power supply and ground terminals of integrated circuits, in order to provide for analysis of electrical characteristics of equipment.

- 1) To standardize in order to solve current problems and in order to extend capabilities of analysis, on the basis of results of the past standardization activities.

- 2) To define more flexible description rules for electric circuits in order to provide more accurate analysis of printed circuit board.

- 3) To introduce the concept of modeling levels to exchange relevant data for each application.

- 4) To enhance electrical modeling for packages and modules.

#### 2 Normative references iTeh STANDARD PREVIEW

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC TS 62404:2007

IEC 62014-1:2001, ht Electronics. designtal automationst/libraries-a078Part b927-Input/output buffer information specifications (IBIS version 53.2)9/iec-ts-62404-2007

### 3 Terms and definitions

Under consideration

#### 4 Outline

#### 4.1 General

The outline of this model is shown in Figure 1.

#### 4.2 Covered range of model

The model is described as circuits covering the whole  $or_{da}$  part of the line 1/2 buffers and the package.

#### 4.3 Language for circuits

The circuits shall be described in extended SPICE format. The structure allows describing simple buffers, complex buffers, power and ground lines, packages and complex memory module boards in a unified format.

#### 4.4 Device model

The characteristics of non-linear devices redescribed in one-dimensional, two-dimensional or three-dimensional table format.

#### 4.5 Structure of model

The data of the model consists of integrated circuit, package and module portions. Therefore each portion can be generated independently.

#### 4.6 Simulation

The netlist of printed circuit board and the I/O buffer model defined by this specification provides accurate circuit simulation results.

#### 4.7 Relation to IBIS

Tools that can extract IBIS data from this model are possible to develop.

#### 5 Model structure

The model shall describe the inside of ICs, packages and module boards as shown in Figure 2.

The models of IC, package and module board consist of the elements given in Table 1.

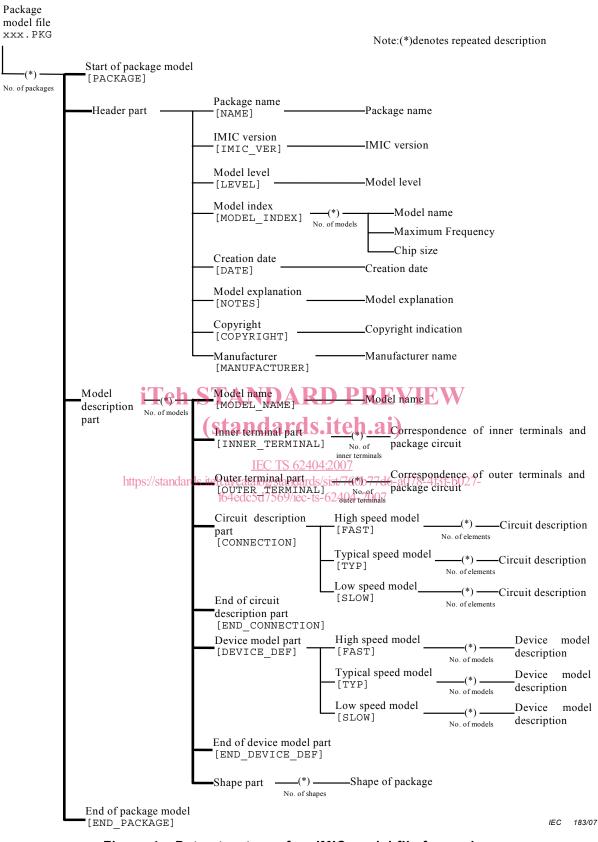

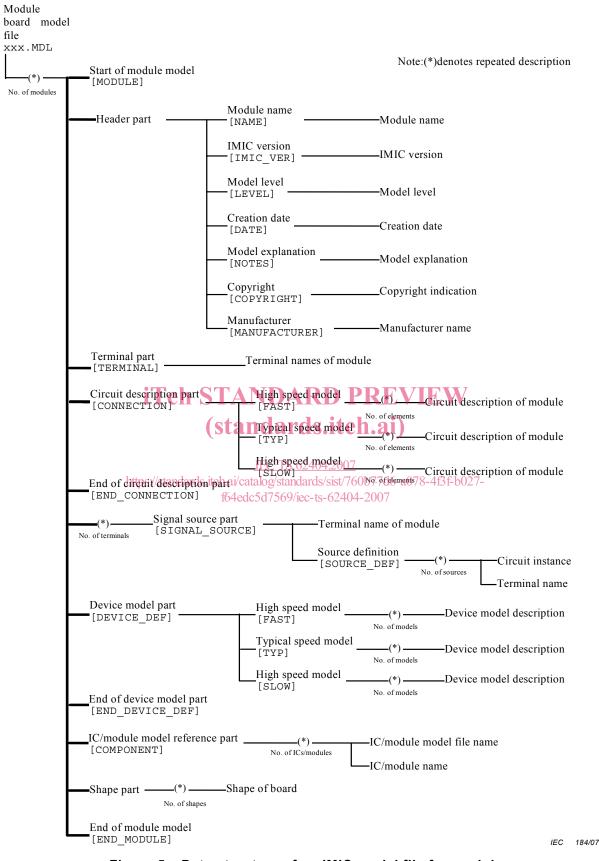

The data structures of IC, package and module board models are shown in Figure 3, Figure 4, and Figure 5, respectively.

Figure 2 – Hierarchy of three models

| File          | Element                                                      | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IC model file | Header                                                       | IC type, model version, model level.                                                                                                                                           |

|               | External terminals                                           | IC external terminals (package pins).                                                                                                                                          |

|               | Pad assignment                                               | Connection between IC pads and package inner terminals.                                                                                                                        |

|               | Circuit description                                          | Internal circuits and their connections.                                                                                                                                       |

|               | Input stimulus assignment                                    | Internal circuits and their stimuli to generate output waveforms.                                                                                                              |

|               | Input stimulus                                               | Input waveforms.                                                                                                                                                               |

|               | Device model                                                 | Characteristics of non-linear circuits in one-<br>dimensional, two-dimensional and three-<br>dimensional table data. Non-linear devices are<br>transistors, diodes and so on.  |

|               | Package model reference                                      | Name of the package model to be used.                                                                                                                                          |

| Package model | Header                                                       | Package name, model version, model level.                                                                                                                                      |

| file          | Model name                                                   | List of models in package circuit model.                                                                                                                                       |

|               | Inner terminal                                               | Cross-reference between internal terminals and package internal circuit model.                                                                                                 |

| i             | Outer terminal<br><b>Feh STANDARI</b><br>Circuit description | Cross-reference between external circuit and<br>package internal circuit model.<br>Internal circuits and their connections.                                                    |

|               | Device <b>forteandards.</b><br><u>IEC TS 62404</u>           | Characteristics of non-linear circuits in one-<br>dimensional, two-dimensional and three-<br>dimensional table data. Non-linear devices are<br>2transistors, diodes and so on. |

| https://      | standards.iteh.ai/catalog/standards/s                        | Material, position, three-dimensional structures.                                                                                                                              |

| Module model  | Header                                                       | Module name, model version, model level.                                                                                                                                       |

| file          | External terminals                                           | External terminals (pins) of module.                                                                                                                                           |

|               | Circuit description                                          | Internal circuits and their connections.                                                                                                                                       |

|               | Signal source                                                | Internal circuits and their terminals to generate output waveforms at corresponding external terminals.                                                                        |

|               | Device model                                                 | Characteristics of non-linear circuits in one-<br>dimensional, two-dimensional and three-<br>dimensional table data. Non-linear devices are<br>transistors, diodes and so on.  |

|               | IC/Module model reference                                    | Names of IC/module model files and model names to be used.                                                                                                                     |

|               | Structure                                                    | Material, position, three-dimensional structures.                                                                                                                              |

Table 1 – Elements of model structures

Figure 3 – Data structure of an IMIC model file for IC

Figure 4 – Data structure of an IMIC model file for package

#### TS 62404 © IEC:2007(E)

Figure 5 – Data structure of an IMIC model file for module