Edition 3.1 2021-06 CONSOLIDATED VERSION

## INTERNATIONAL STANDARD

Semiconductor devices – Discrete devices – PREVIEW

Part 8: Field-effect transistors

IEC 60747-8:2010

#### THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2021 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland

Tel.: +41 22 919 02 11 info@iec.ch

www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigendum or an amendment might have been published.

#### IEC publications search - webstore.iec.ch/advsearchform

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee, ...). It also gives information on projects, replaced and withdrawn publications.

**IEC Just Published - webstore.iec.ch/justpublished**Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and once a month by email.

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need further assistance, please contact the Customer Service Centre: sales@iec.ch.

#### IEC online collection - oc.iec.ch

Discover our powerful search engine and read freely all the publications previews. With a subscription you will always have access to up to date content tailored to your needs.

#### Electropedia - www.electropedia.org

The world's leading online dictionary on electrotechnology, containing more than 22 000 terminological entries in English and French, with equivalent terms in 18 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

747-8:2010

Edition 3.1 2021-06 CONSOLIDATED VERSION

## INTERNATIONAL STANDARD

Semiconductor devices – Discrete devices – PREVIEW

Part 8: Field-effect transistors

IEC 60747-8:2010

https://standards.iteh.ai/catalog/standards/sist/fc8aaa7f-7c16-4f85-ae41-3006f6c90235/iec-60747-8-2010

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.080.30 ISBN 978-2-8322-9959-3

Warning! Make sure that you obtained this publication from an authorized distributor.

# iTeh STANDARD PREVIEW (standards.iteh.ai)

IEC 60747-8:2010

Edition 3.1 2021-06 CONSOLIDATED VERSION

## **REDLINE VERSION**

Semiconductor devices – Discrete devices – PRE VIEW

Part 8: Field-effect transistors

IEC 60747-8:2010

### CONTENTS

| FO | DREWORD                               |                               |                                                                                                  |          |  |  |

|----|---------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------|----------|--|--|

| 1  | Scop                                  | e                             |                                                                                                  | 8        |  |  |

| 2  | Normative references                  |                               |                                                                                                  |          |  |  |

| 3  | Terms and definitions                 |                               |                                                                                                  |          |  |  |

|    | 3.1                                   | Types                         | of field-effect transistors                                                                      | 9        |  |  |

|    | 3.2                                   |                               | al terms                                                                                         |          |  |  |

|    |                                       | 3.2.1                         | Physical regions (of a field-effect transistor)                                                  |          |  |  |

|    |                                       | 3.2.2                         | Functional regions                                                                               |          |  |  |

|    | 3.3                                   | Terms                         | related to ratings and characteristics                                                           |          |  |  |

|    | 3.4                                   | Conve                         | ntional used terms                                                                               | 17       |  |  |

| 4  | Letter symbols                        |                               |                                                                                                  |          |  |  |

|    | 4.1 General                           |                               |                                                                                                  |          |  |  |

|    | 4.2                                   | Additional general subscripts |                                                                                                  | 17       |  |  |

|    | 4.3                                   |                               | letter symbols                                                                                   |          |  |  |

|    |                                       | 4.3.1                         | Voltage                                                                                          | 17       |  |  |

|    |                                       | 4.3.2                         | Currents                                                                                         | 18       |  |  |

|    |                                       | 4.3.3                         | Power dissipation                                                                                | 19       |  |  |

|    |                                       | 4.3.4                         | Small-signal parameters                                                                          | 19       |  |  |

|    |                                       | 4.3.5                         | Other parameters                                                                                 |          |  |  |

|    |                                       | 4.3.6                         | Matched-pair field-effect transistors                                                            | 21       |  |  |

|    |                                       | 4.3.7                         | Inverse diodes integrated in MOSFETs for N-channel                                               | 21       |  |  |

| 5  | Essential ratings and characteristics |                               |                                                                                                  |          |  |  |

|    | 5.1s:                                 | Gener                         | als.iteh.ai/catalog/standards/sist/fc8aaa7f-7c1.6-4f85-ae41-3006f6c90235                         | /iec+ 22 |  |  |

|    |                                       | 5.1.1                         | Device categories                                                                                | 22       |  |  |

|    |                                       | 5.1.2                         | Multiple-gate devices                                                                            | 22       |  |  |

|    |                                       | 5.1.3                         | Handling precautions                                                                             | 22       |  |  |

|    | 5.2                                   | Rating                        | s (limiting values)                                                                              | 22       |  |  |

|    |                                       | 5.2.1                         | Temperatures                                                                                     | 22       |  |  |

|    |                                       | 5.2.2                         | Power dissipation (Ptot)                                                                         | 22       |  |  |

|    |                                       | 5.2.3                         | Safe operating area (SOA) for MOSFET only                                                        |          |  |  |

|    |                                       | 5.2.4                         | Voltages and currents                                                                            | 23       |  |  |

|    | 5.3                                   | Chara                         | cteristics                                                                                       |          |  |  |

|    |                                       | 5.3.1                         | Characteristics for low-frequency amplifier                                                      |          |  |  |

|    |                                       | 5.3.2                         | Characteristics for high-frequency amplifier                                                     |          |  |  |

|    |                                       | 5.3.3                         | Characteristics for high and low power switching and chopper                                     |          |  |  |

|    |                                       | 5.3.4                         | Characteristics for low-level amplifier                                                          |          |  |  |

|    |                                       | 5.3.5                         | Characteristics for voltage-controlled resistor                                                  | 32       |  |  |

|    |                                       | 5.3.6                         | Specific characteristics of matched-pair field-effect transistors for low-frequency differential | 33       |  |  |

| 6  | Measuring methods                     |                               |                                                                                                  |          |  |  |

|    | 6.1 General                           |                               |                                                                                                  |          |  |  |

|    | 6.2                                   | Verific                       | ation of ratings (limiting values)                                                               | 34       |  |  |

|    |                                       | 6.2.1                         | Voltages and currents                                                                            | 34       |  |  |

|    |                                       | 6.2.2                         | Safe operating area                                                                              | 40       |  |  |

|    |                                       | 6.2.3                         | Avalanche energy                                                                                 | 45       |  |  |

|     | 6.3     | Methods of measurement |                                                                                                                              | 4 / |  |  |

|-----|---------|------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

|     |         | 6.3.1                  | Breakdown voltage, drain to source (V(BR)DS*)                                                                                | 47  |  |  |

|     |         | 6.3.2                  | Gate-source off-state voltage (VGS(off)) (type A and B), gate source threshold voltage (VGS(th)) (type C)                    |     |  |  |

|     |         | 6.3.3                  | Drain leakage current (d.c.) (IDS*)(type C), Drain cut-off current (d.c.) (IDSX) (type A and B)                              |     |  |  |

|     |         | 6.3.4                  | Gate cut-off current (IGS*)(type A), Gate-leakage current (IGS*)(type B and C)                                               | 49  |  |  |

|     |         | 6.3.5                  | (Static) drain-source on-state resistance $(r_{DS(on)})$ or drain-source on-state voltage $(V_{DS(on)})$                     |     |  |  |

|     |         | 6.3.6                  | Switching times ( $t_{d(on)}$ , $t_{r}$ , $t_{d(off)}$ , and $t_{f}$ )                                                       | 52  |  |  |

|     |         | 6.3.7                  | Turn-on power dissipation $(P_{on})$ , turn-on energy (per pulse) $(E_{on})$                                                 |     |  |  |

|     |         | 6.3.8                  | Turn-off power dissipation ( $P_{\text{Off}}$ ), turn-off energy (per pulse) ( $E_{\text{Off}}$ )                            | 54  |  |  |

|     |         | 6.3.9                  | Gate charges (QG, QGD, QGS(th), QGS(pI))                                                                                     | 54  |  |  |

|     |         | 6.3.10                 | Common source short-circuit input capacitance (Ciss)                                                                         |     |  |  |

|     |         |                        | Common source short-circuit output capacitance (Coss)                                                                        |     |  |  |

|     |         | 6.3.12                 | Common source short-circuit reverse transfer capacitance $(C_{rss})$                                                         | 57  |  |  |

|     |         | 6.3.13                 | Internal gate resistance (r <sub>q</sub> )                                                                                   | 58  |  |  |

|     |         | 6.3.14                 | MOSFET forward recovery time ( $t_{fr}$ ) and MOSFET forward recovered charge ( $Q_f$ )                                      | 59  |  |  |

|     |         | 6.3.15                 | Drain-source reverse voltage ( <del>V<sub>DSR</sub></del> V <sub>SD</sub> )                                                  | 64  |  |  |

|     |         | 6.3.16                 | Small-signal short-circuit output conductance (type A, B and C) (goss)                                                       | 64  |  |  |

|     |         | 6.3.17                 | Small-signal short-circuit forward transconductance (types A, B and C)                                                       | 67  |  |  |

|     |         | 6.3.18                 | Noise (types A, B and C) (F, Vn)                                                                                             | 69  |  |  |

|     |         |                        | On-state drain-source resistance (under small-signal conditions)  (rds(on))                                                  |     |  |  |

|     |         | 6.3.20                 | Channel-case transient thermal impedance $(Z_{th(j-c)})$ and thermal resistance $(R_{th(j-c)})$ of a field-effect transistor |     |  |  |

| 7   | Acce    | ptance                 | and reliability                                                                                                              |     |  |  |

|     | 7.1     | ·                      |                                                                                                                              |     |  |  |

|     | 7.2     |                        |                                                                                                                              |     |  |  |

|     | 7.3     |                        | ance and reliability tests                                                                                                   |     |  |  |

|     |         | 7.3.1                  | High-temperature blocking (HTRB)                                                                                             | 74  |  |  |

|     |         | 7.3.2                  | High-temperature gate bias                                                                                                   |     |  |  |

|     |         | 7.3.3                  | Intermittent operating life (load cycles)                                                                                    |     |  |  |

|     | 7.4     | Type to                | ests and routine tests                                                                                                       |     |  |  |

|     |         | 7.4.1                  | Type tests                                                                                                                   | 75  |  |  |

|     |         | 7.4.2                  | Routine tests                                                                                                                |     |  |  |

| Bib | oliogra | phy                    |                                                                                                                              | 77  |  |  |

| Fig | gure 1  | – Basic                | waveforms to specify the gate charges                                                                                        | 14  |  |  |

| Fig | gure 2  | – Integr               | al times for the turn-on energy $E_{	extsf{on}}$ and turn-off energy $E_{	extsf{off}}$                                       | 16  |  |  |

|     |         |                        | hing times                                                                                                                   |     |  |  |

| _   |         |                        | t diagram for testing of drain-source voltage                                                                                |     |  |  |

|     |         |                        | t diagram for testing of gate-source voltage                                                                                 |     |  |  |

|     |         |                        |                                                                                                                              |     |  |  |

| _   |         |                        | t diagram for testing of gate-drain voltage                                                                                  |     |  |  |

| ьlб | jure /  | – Rasic                | circuit for the testing of drain current                                                                                     | 3/  |  |  |

| Figure 8 – Circuit diagram for testing of peak drain current                                                                                               | 38 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 9 – Basic circuit for the testing of reverse drain current of MOSFETs                                                                               | 38 |

| Figure 10 – Basic circuit for the testing of peak reverse drain current of MOSFETs                                                                         | 39 |

| Figure 11 – Circuit diagram for verifying FBSOA                                                                                                            | 40 |

| Figure 12 – Circuit diagram for verifying RBSOA                                                                                                            |    |

| Figure 13 – Test waveforms for verifying RBSOA                                                                                                             |    |

| Figure 14 – Circuit for testing safe operating pulse duration at load short circuit                                                                        | 43 |

| Figure 15 – Waveforms of gate-source voltage VGS, drain current ID and voltage VDS during load short circuit condition SCSOA                               | 43 |

| Figure 16 – Circuit for the inductive avalanche switching                                                                                                  | 45 |

| Figure 17 – Waveforms of $I_{\text{D}}$ , $V_{\text{DS}}$ and $V_{\text{GS}}$ during unclamped inductive switching                                         | 45 |

| Figure 18 – Waveforms of $I_{\hbox{\scriptsize D}},\ V_{\hbox{\scriptsize DS}}$ and $V_{\hbox{\scriptsize GS}}$ for the non-repetitive avalanche switching | 46 |

| Figure 19 - Circuit diagrams for the measurement drain-source breakdown voltage                                                                            | 47 |

| Figure 20 – Circuit diagram for measurement of gate-source off-state voltage and gate-source threshold voltage                                             | 48 |

| Figure 21 – Circuit diagram for drain leakage (or off-state) current or drain cut-off current measurement                                                  | 49 |

| Figure 22 – Circuit diagram for measuring of gate cut-off current or gate leakage current                                                                  | 50 |

| Figure 23 – Basic circuit of measurement for on-state resistance                                                                                           | 51 |

| Figure 24 – On-state resistance                                                                                                                            | 51 |

| Figure 25 – Circuit diagram for switching time                                                                                                             | 52 |

| Figure 26 – Schematic switching waveforms and times                                                                                                        | 52 |

| Figure 27 – Circuit for determining the turn-on and turn-off power dissipation and/or                                                                      |    |

| energy 60747-8-2010                                                                                                                                        |    |

| Figure 28 – Circuit diagrams for the measurement gate charges                                                                                              |    |

| Figure 29 – Basic for the measurement of short-circuit input capacitance                                                                                   |    |

| Figure 30 – Basic circuit for measurement of short-circuit output capacitance $(C_{OSS})$                                                                  |    |

| Figure 31 – Circuit for measurement of reverse transfer capacitance $C_{rss}$                                                                              |    |

| Figure 32 – Circuit for measurement of internal gate resistance                                                                                            | 59 |

| Figure 33 – Circuit diagram for MOSFET forward recovery time and recovered charge (Method 1)                                                               | 60 |

| Figure 34 – Current waveform through MOSFET (Method 1)                                                                                                     | 61 |

| Figure 35 – Circuit diagram for MOSFET forward recovery time and recovered charge (Method 2)                                                               | 62 |

| Figure 36 - Current waveform through MOSFET (Method 2)                                                                                                     | 63 |

| Figure 37 – Circuit diagram for the measurement of drain-source reverse voltage                                                                            | 64 |

| Figure 38 – Basic circuit for the measurement of the output conductance $g_{\rm OSS}$ (method 1: null method)                                              | 65 |

| Figure 39 – Basic circuit for the measurement of the output conductance $g_{\rm OSS}$ (method 2: two-voltmeter method)                                     | 66 |

| Figure 40 – Circuit for the measurement of short-circuit forward transconductance $g_{fS}$ (Method 1: Null method)                                         | 67 |

| Figure 41 – Circuit for the measurement of forward transconductance $g_{fS}$ (method 2: two-voltmeter method)                                              | 68 |

| Figure 42 – Block diagram for the measurement of equivalent input noise voltage                                                                            | 69 |

| © IEC 2021                                                                                                                                         |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 43 – Circuit for the measurement of equivalent input noise voltage                                                                          | 69 |

| Figure 44 – Circuit diagram for the measurement of on-state drain-source resistance                                                                | 70 |

| Figure 45 – Circuit diagram                                                                                                                        | 71 |

| Figure 46 – Circuit for high-temperature blockings                                                                                                 | 74 |

| Figure 47 – Circuit for high-temperature gate bias                                                                                                 | 74 |

| Figure 48 – Circuit for intermittent operating life                                                                                                | 75 |

| Table 1 – Terms for MOSFET in this standard document and the conventional used terms for the inverse diode integrated in the MOSFETs for N-channel | 17 |

| Table 2 – Acceptance defining characteristics                                                                                                      | 34 |

| Table 3 – Acceptance-defining characteristics for endurance and reliability tests                                                                  | 73 |

| Table 4 – Minimum type and routine tests for FETs when applicable                                                                                  | 76 |

# iTeh STANDARD PREVIEW (standards.iteh.ai)

#### IEC 60747-8:2010

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

## SEMICONDUCTOR DEVICES – DISCRETE DEVICES –

Part 8: Field-effect transistors

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

This consolidated version of the official IEC Standard and its amendment has been prepared for user convenience.

IEC 60747-8 edition 3.1 contains the third edition (2010-12) [documents 47E/398/FDIS and 47E/406/RVD] and its amendment 1 (2021-06) [documents 47E/726/CDV and 47E/744/RVC].

In this Redline version, a vertical line in the margin shows where the technical content is modified by amendment 1. Additions are in green text, deletions are in strikethrough red text. A separate Final version with all changes accepted is available in this publication.

International Standard IEC 60747-8 has been prepared by subcommittee 47E: Discrete semiconductor devices, of IEC technical committee 47: Semiconductor devices.

This third edition constitutes a technical revision.

The main changes with respect to the previous edition are listed below.

- a) "Clause 3 Classification" was moved and added to Clause 1.

- b) "Clause 4 Terminology and letter symbols" was divided into "Clause 3 Terms and definitions" and "Clause 4 Letter symbols" was amended with additions and deletions.

- c) Clause 5, 6 and 7 were amended with necessary additions and deletions.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

This Part 8 should be used in conjunction with IEC 60747-1:2006.

A list of all the parts in the IEC 60747 series, under the general title *Semiconductor devices* – *Discrete devices*, can be found on the IEC website.

Future standards in this series will carry the new general title as cited above. Titles of existing standards in this series will be updated at the time of the next edition.

The committee has decided that the contents of the base publication and its amendment will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- IEC 60747-8:2010

- replaced by a revised edition, or ndards/sist/fc8aaa7f-7c16-4f85-ac41-3006f6c90235/icc-

- amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

## SEMICONDUCTOR DEVICES – DISCRETE DEVICES –

#### Part 8: Field-effect transistors

#### 1 Scope

This part of IEC 60747 gives standards for the following categories of field-effect transistors:

- type A: junction-gate type;

- type B: insulated-gate depletion (normally on) type;

- type C: insulated-gate enhancement (normally off) type.

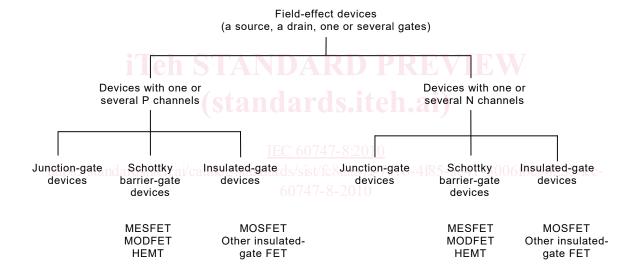

Since a field-effect transistor may have one or several gates, the classification shown below results:

NOTE 1 Schottky barrier-gate and insulated gate devices include depletion type devices and enhancement type devices.

NOTE 2 MOSFETs for some applications may not have inverse diode characteristics in the data sheet. Special circuit element structures to eliminate body diode are under development for such applications. MOSFET applications such as motor control equipment need to specify the inverse diode characteristics in the MOSFET to use the inverse diode as a free wheeling diode.

NOTE 3 The graphical symbol only for type C is used in this standard. The standard equally applies for P-channel and for type A and B devices.

#### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 61340 (all parts), Electrostatics

IEC 60747-1:2006, Semiconductor devices - Part 1: General

IEC 60747-8:2010+AMD1:2021 CSV © IEC 2021

IEC 60747-7:2000, Semiconductor devices – Part 7: Bipolar transistors

IEC 60749-23:2004, Semiconductor devices – Mechanical and climatic test methods – Part 23: High temperature operating life

**-9-**

IEC 60749-34, Semiconductor devices – Mechanical and climatic test methods – Part 34: Power cycling

#### 3 Terms and definitions

For the purpose of this document, the following terms and definitions apply.

#### 3.1 Types of field-effect transistors

#### 3.1.1

#### N-channel field-effect transistor

field-effect transistor that has one or more N-type conduction channels

#### 3.1.2

#### P-channel field-effect transistor

field-effect transistor that has one or more P-type conduction channels

#### 3.1.3

## junction-gate field-effect transistor JFET

field-effect transistor in which standards. Iteh.all

- the source and drain regions are connected with each other by the channel region, all three being of the same conductivity type;747-82010

- a gate region adjacent to the channel has the opposite conductivity type, thus forming with source, channel and drain region a PN junction

NOTE The gate-source voltage controls the conductivity of the conduction channel in the channel region by controlling the width of the gate space-charge region and hence also the remaining cross-section of the conduction channel.

#### 3.1.4

## insulated-gate field-effect transistor

field-effect transistor in which

- one or more gate electrodes are electrically insulated from the body;

- the conductivity type of both the source and drain regions is opposite from that of the semiconductor body in which they are located;

- the principal current flows in a channel that is formed by an inversion layer connecting source and drain regions

NOTE The inversion layer is either already present at zero gate-source voltage or produced within the body at sufficiently high forward gate-source voltage by accumulation of the minority charge carriers of the body material. The conductance of the channel is controlled by the gate-source voltage, which controls the electric field between gate electrode and the body and hence the amount of accumulated minority charge carriers.

#### 3.1.5

## metal-oxide-semiconductor field-effect transistor MOSFET

insulated-gate field-effect transistor in which the insulating layer between each gate electrode and the channel is oxide material

#### 3.1.6

#### depletion-type (normally on) field-effect transistor

field-effect transistor in which an inversion layer present at the surface of the active semiconductor region causes an appreciable channel conductance that may be increased (decreased) by applying a forward (reverse) gate-source voltage

#### 3.1.7

#### enhancement-type (normally off) field-effect transistor

field-effect transistor having substantially zero channel conductance at zero gate-source voltage, and in which a conduction channel may be obtained by applying a sufficiently high forward gate-source voltage, which induces an inversion layer below the gate electrode

#### 3.1.8

#### single-gate field-effect transistor

field-effect transistor having a gate region, a source region, and a drain region

NOTE The term may be abbreviated to "field-effect transistor", if no ambiguity is likely to occur.

#### 3.1.9

#### dual-gate field-effect transistor

field-effect transistor having two independent gate regions, a source region, and a drain region

#### 3.1.10

### schottky-barrier-gate field-effect transistor

field-effect transistor in which

- the source and drain regions are connected with each other by the channel region, all three being of the same conductivity type;

- one or more gate electrodes each form a Schottky-barrier with the channel region;

the gate-source voltage controls the conductance of the conduction channel by varying its cross-section

#### 3.1.11

#### metal-semiconductor field-effect transistor

#### **MESFET**

Schottky-barrier-gate field-effect transistor in which the gate electrodes are metal

#### 3.1.12

## modulation-doped field-effect transistor or high electron mobility transistor MODFET or HEMT

metal-semiconductor field-effect transistor in which a doped material forms a heterojunction with an undoped channel; the doped material supplies electrons to the undoped channel whose high electron mobility results in enhanced channel conductance

NOTE MODFET and HEMT should be used interchangeably.

#### 3.2 General terms

#### 3.2.1 Physical regions (of a field-effect transistor)

#### 3.2.1.1

#### source (of a field-effect transistor)

physical region that is designed by the manufacturer to contain the supply region under the defined operating conditions to which the specifications refer

© IEC 2021

#### 3.2.1.2

#### drain (of a field-effect transistor)

physical region that is designed by the manufacturer to contain the collection region under the defined operating conditions to which the specifications refer

#### 3.2.1.3

#### gate (of an IGFET)

insulating layer between the gate electrode and the surface of the semiconductor body, below which the channel is or may be formed

#### 3.2.1.4

#### gate (of an JFET)

region below the gate electrode that is of opposite conductivity type from that of the source, channel and drain regions

#### 3.2.1.5

#### channel (of a depletion-type IGFET)

inversion layer technologically placed below the gate region

#### 3.2.1.6

#### channel (of a JFET)

region between source region and drain region that has the same conductivity type as these two regions

#### 3.2.1.7

#### subchannel (of an IGFET)

region between source region and drain region, excluding the channel region of a depletiontype IGFET and all pertinent transition zones

#### 3.2.1.8

#### substrate (of a JFET or IGFET) standards/sist/fe8aaa7f-7c16-4f85-ae41-3006f6c90235/iec-

part of the original material that remains unchanged when the device elements are formed upon or within the original material

NOTE The original material may be a layer of semiconductor material cut from a single crystal, a layer of semiconductor material deposited on a supporting base, or the supporting base itself.

#### 3.2.1.9

#### substrate (of a JFET or IGFET)

original semiconductor material before being processed

NOTE The intended meaning will become clear from the context in which the term is used. If necessary, distinction could be made between the "original substrate" and the "remaining substrate".

#### 3.2.1.10

#### substrate (of a thin-film field-effect transistor)

insulator that supports the source and drain electrodes, the insulating gate layer, and the thin semiconductor layer

#### 3.2.2 Functional regions

#### 3.2.2.1

#### functional source region

supply region that delivers principal-current charge carriers into the channel

#### 3.2.2.2

#### functional drain region

collection region that acquires principal-current charge carriers from the channel