Edition 1.0 2008-10

# INTERNATIONAL STANDARD

EMC IC modelling – Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted emissions modelling (ICEM-CE)

https://standards.itel

586-2ffd-4bb3-9c9c-d8b1c723b596/iec-

# THIS PUBLICATION IS COPYRIGHT PROTECTED

#### Copyright © 2008 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland Email: inmail@iec.ch Web: www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Rease make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: <u>www.iec.ch/searchpub</u>

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: www.iec.ch/online\_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

Electropedia: <u>www.electropedia.org</u>

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

• Customer Service Centre: www.iec.ch/webstore/custserv If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: csc@iec.ch Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

Edition 1.0 2008-10

# INTERNATIONAL STANDARD

EMC IC modelling – Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted emissions modelling (ICEM-CE)

https://standards.iteh.a

586-2ffd-4bb3-9c9c-d8b1c723b596/iec-

INTERNATIONAL ELECTROTECHNICAL COMMISSION

PRICE CODE

ICS 31.200

ISBN 978-2-88910-702-5

Х

# CONTENTS

| FOREWORD                                                        |                                                                         |                                                                                                                                        |      |  |  |  |

|-----------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|--|--|--|

| 1                                                               | 1 Scope                                                                 |                                                                                                                                        |      |  |  |  |

| 2                                                               | Norm                                                                    | Normative references                                                                                                                   |      |  |  |  |

| 3                                                               | Term                                                                    | s and definitions                                                                                                                      | 7    |  |  |  |

| 4                                                               | Philosophy                                                              |                                                                                                                                        |      |  |  |  |

|                                                                 | 4.1                                                                     | General                                                                                                                                | 8    |  |  |  |

|                                                                 | 4.2                                                                     | Conducted emission from core activity (digital culprit)                                                                                | 8    |  |  |  |

|                                                                 | 4.3                                                                     | Conducted emission from I/O activity                                                                                                   |      |  |  |  |

| 5                                                               | Basio                                                                   | components                                                                                                                             | 9    |  |  |  |

|                                                                 | 5.1                                                                     | General                                                                                                                                | 9    |  |  |  |

|                                                                 | 5.2                                                                     | Internal Activity (IA)                                                                                                                 | . 9  |  |  |  |

|                                                                 | 5.3                                                                     | Passive Distribution Network (PDN)                                                                                                     | . 10 |  |  |  |

| 6 IC macro-models                                               |                                                                         |                                                                                                                                        | 12   |  |  |  |

|                                                                 | 6.1                                                                     | General<br>General IC macro-model<br>Block-based IC macro-model<br>6.3.1 Block component<br>6.3.2 Inter-Block Coupling component (IBC) | . 12 |  |  |  |

|                                                                 | 6.2                                                                     | General IC macro-model                                                                                                                 | . 12 |  |  |  |

|                                                                 | 6.3                                                                     | Block-based IC macro-model                                                                                                             | . 13 |  |  |  |

|                                                                 |                                                                         | 6.3.1 Block component                                                                                                                  | .13  |  |  |  |

|                                                                 |                                                                         | 6.3.2 Inter-Block Coupling component (IBC)                                                                                             | .14  |  |  |  |

|                                                                 |                                                                         | 6.3.3 Block-based IC macro-model structure                                                                                             | . 15 |  |  |  |

|                                                                 | 6.4                                                                     | Sub-model-based IC macro-model                                                                                                         | . 17 |  |  |  |

|                                                                 |                                                                         | 6.4.1 Sub-model component                                                                                                              |      |  |  |  |

|                                                                 |                                                                         | 6.4.2 Sub-model-based IC macro-model structure                                                                                         |      |  |  |  |

| 7                                                               |                                                                         | irements for parameter extraction                                                                                                      |      |  |  |  |

|                                                                 | 7.1                                                                     | General                                                                                                                                |      |  |  |  |

|                                                                 | 7.2                                                                     | Environmental extraction constraints                                                                                                   |      |  |  |  |

|                                                                 | 7.3                                                                     | IA parameter extraction                                                                                                                |      |  |  |  |

|                                                                 | 7.4                                                                     | PDN parameter extraction .                                                                                                             |      |  |  |  |

|                                                                 | 7.5                                                                     | IBC parameter extraction                                                                                                               |      |  |  |  |

|                                                                 |                                                                         | (informative) Model parameter generation                                                                                               |      |  |  |  |

|                                                                 |                                                                         | (informative) Decoupling capacitors optimization                                                                                       | . 38 |  |  |  |

|                                                                 |                                                                         | (informative) Conducted emission prediction                                                                                            |      |  |  |  |

| Anr                                                             | nex D                                                                   | (informative) Conducted emission prediction at PCB level                                                                               | .41  |  |  |  |

| Bibl                                                            | liogra                                                                  | phy                                                                                                                                    | .43  |  |  |  |

|                                                                 |                                                                         |                                                                                                                                        |      |  |  |  |

| Figu                                                            | ure 1                                                                   | <ul> <li>Decomposition example of a digital IC for conducted emissions analysis</li> </ul>                                             | 8    |  |  |  |

| Figu                                                            | ure 2                                                                   | – IA component                                                                                                                         | 9    |  |  |  |

| Fia                                                             | ure 3                                                                   | - Example of IA characteristics in time domain                                                                                         | . 10 |  |  |  |

| -                                                               |                                                                         | -                                                                                                                                      |      |  |  |  |

| Figure 4 – Example of IA characteristics in frequency domain    |                                                                         |                                                                                                                                        |      |  |  |  |

| Figure 5 – Example of a four-terminal PDN using lumped elements |                                                                         |                                                                                                                                        |      |  |  |  |

| -                                                               | Figure 6 – Example of a seven-terminal PDN using distributed elements   |                                                                                                                                        |      |  |  |  |

| -                                                               | Figure 7 – Example of a twelve-terminal PDN using matrix representation |                                                                                                                                        |      |  |  |  |

| Figure 8 – General IC macro-model1                              |                                                                         |                                                                                                                                        |      |  |  |  |

| Figure 9 – Example of block component1                          |                                                                         |                                                                                                                                        |      |  |  |  |

| Figure 10 – Example of block components for I/Os14              |                                                                         |                                                                                                                                        |      |  |  |  |

| -                                                               |                                                                         |                                                                                                                                        |      |  |  |  |

| Figure 11 – Example of IBC with two internal terminals                          | 15 |

|---------------------------------------------------------------------------------|----|

| Figure 12 – Relationship between blocks and IBC                                 | 15 |

| Figure 13 – Block-based IC macro-model                                          | 16 |

| Figure 14 – Example of block-based IC macro-model                               | 17 |

| Figure 15 – Example of simple sub-model                                         | 18 |

| Figure 16 – Sub-model-based IC macro-model                                      | 18 |

| Figure A.1 – Typical characterization current gate schematic                    | 22 |

| Figure A.2 – Current peak during switching transition                           | 22 |

| Figure A.3 – Example of IA extraction procedure from design                     | 23 |

| Figure A.4 – Technology Influence                                               | 23 |

| Figure A.5 – Final current waveform for a program period                        | 24 |

| Figure A.6 – Comparison between measurement and simulation                      | 24 |

| Figure A.7 – Lumped element model of a package                                  | 25 |

| Figure A.8 – Circuit structure of the netlist                                   | 26 |

| Figure A.9 – Principle of the IA computation                                    | 27 |

| Figure A.10 – Process involved to model i <sub>A</sub> (t)                      | 27 |

| Figure A.11 – i <sub>Ext</sub> (t) measured using IEC 61967-4.                  | 28 |

| Figure A.12 – i <sub>A</sub> (t)and i <sub>Ext</sub> (t) profiles               | 28 |

| Figure A.13 – Example of a hardware set-up used to extract the PDN parameters   | 30 |

| Figure A.14 – Miniature 50 $\Omega$ coaxial connectors                          | 30 |

| Figure A.15 – Impedance probe using two miniature coaxial connectors            | 31 |

| Figure A.16 – Open and short terminations                                       | 31 |

| Figure A.17 – Measurement probe model                                           | 31 |

| Figure A.18 – De-embedding principle                                            | 32 |

| Figure A.19 – Example of a predefined PDN structure                             | 33 |

| Figure A.20 – RL configuration                                                  | 34 |

| Figure A.21 – RLC configuration                                                 | 34 |

| Figure A.22 - RLC with magnetic coupling configuration                          | 35 |

| Figure A.23 - Impedance seen from Vcc and Gnd                                   | 35 |

| Figure A.24 - Complete PDN component                                            | 36 |

| Figure A.25 – Set-up for correlation (left), measurement and prediction (right) | 37 |

| Figure A.26 – Set-up used to measure the internal decoupling capacitor          | 37 |

| Figure B.1 – Equivalent schematic of the complete electronic system             | 38 |

| Figure B.2 – Impedance prediction and measurements                              | 39 |

| Figure C.1 – IEC 61967-4 test set-up standard                                   | 40 |

| Figure C.2 – Comparison between prediction and measurement                      | 40 |

| Figure D.1 – Prediction of the Vdcc noise level at PCB level                    | 41 |

| Figure D.2 – Good agreements on the noise envelope                              | 42 |

| Table A.1 – Typical parameters for CMOS logic technologies          | 20 |

|---------------------------------------------------------------------|----|

| Table A.2 – Typical number of logic gates vs. CPU technology        | 21 |

| Table A.3 – R, L and C parameters for various package types         | 21 |

| Table A.4 – Measurement configurations and extracted RLC parameters | 33 |

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### EMC IC MODELLING -

# Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted emissions modelling (ICEM-CE)

#### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62433-2 has been prepared by subcommittee 47A: Integrated circuits, of IEC technical committee 47: Semiconductor devices.

The text of this standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 47A/794/FDIS | 47A/799/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all the parts in the IEC 62433 series, under the general title *EMC IC modelling*, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

A bilingual version of this publication may be issued at a later date.

|                                                                              | $\langle \langle \langle \rangle \rangle$ |

|------------------------------------------------------------------------------|-------------------------------------------|

|                                                                              |                                           |

|                                                                              |                                           |

|                                                                              | $\searrow$                                |

| iTeh STAKDARI IR                                                             | EVIEW                                     |

| (stan fards itch.a                                                           | i)                                        |

|                                                                              |                                           |

| https://standards.iteh.av/ataly/standards/st/7550d586-2ffd-4t<br>0843>2-2008 |                                           |

|                                                                              |                                           |

|                                                                              |                                           |

|                                                                              |                                           |

|                                                                              |                                           |

## EMC IC MODELLING -

# Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted emissions modelling (ICEM-CE)

#### 1 Scope

This part of IEC 62433 specifies macro-models for ICs to simulate conducted electromagnetic emissions on a printed circuit board. The model is commonly called Integrated Circuit Emission Model - Conducted Emission (ICEM-CE).

The ICEM-CE model can also be used for modelling an IC-die, a functional block and an Intellectual Property block (IP).

The ICEM-CE model can be used to model both digital and analogue ICs.

Basically, conducted emissions have two origins:

- conducted emissions through power supply terminals and ground reference structures;

- conducted emissions through input/output (I/O) terminals.

The ICEM-CE model addresses those two types of origins in a single approach.

This standard defines structures and components of the macro-model for EMI simulation taking into account the IC's internal activities.

This standard gives general data, which can be implemented in different formats or languages such as IBIS, IMIC, SPICE, VHDL-AMS and Verilog. SPICE is however chosen as default simulation environment to cover all the conducted emissions.

This standard also specifies requirements for information that shall be incorporated in each ICEM-CE model or component part of the model for model circulation, but description syntax is not within the scope of this standard.

## 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 61967 (all parts), Integrated Circuits – Measurement of electromagnetic emissions, 150 KHz to 1 GHz

IEC 61967-4, Integrated circuits – Measurement of electromagnetic emissions, 150 kHz to 1 GHz – Part 4: Measurement of conducted emissions – 1  $\Omega$ /150  $\Omega$  direct coupling method

### 3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

## 3.1

#### external terminal

terminal of an IC macro-model, which interfaces the model to the external environment of the IC, such as power supply pins and I/O pins

NOTE In this document, the name of each external terminal starts with "ET".

#### 3.2

#### internal terminal

terminal of an IC macro-model's component, which interfaces the component to other components of the IC macro-model

NOTE In this document, the name of each internal terminal starts with "IT".

## 4 Philosophy

#### 4.1 General

Integrated circuits will have more and more gates on silicon and technical progress will develop faster. To predict the electromagnetic behaviour of equipment, it is required to model the switching of the input and output interface and the internal activities of an integrated circuit effectively.

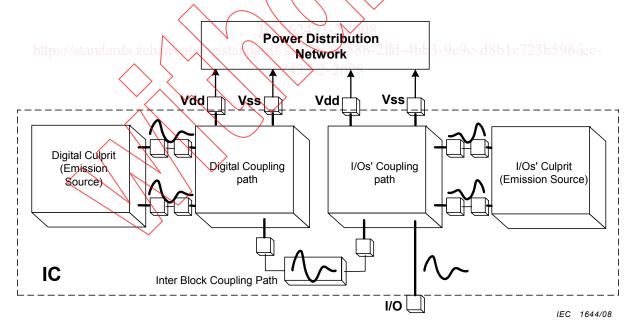

Figure 1 depicts an example of decomposition of an IC to enable conducted emissions analysis. The internal digital activity (culprit) is a source of electromagnetic noise that originates in switching of active devices. The coupling path propagates the emissions to the IC's external terminals: pins/pads. The coupling path is the power distribution network or I/O lines inside the IC.

#### Figure 1 – Decomposition example of a digital IC for conducted emissions analysis

#### 4.2 Conducted emission from core activity (digital culprit)

The current transients are created in the core area on the IC-die. Due to the characteristics of the digital coupling paths, the passive distribution network on printed circuit board (PCB) and the availability of on-chip decoupling, a portion of these current transients will occur at the power supply pins of the IC.

NOTE These off-chip power supply currents can be measured according to the IEC 61967 series.

#### Conducted emission from I/O activity 4.3

I/Os activities may create voltage fluctuations of power and ground levels, and conducted emissions appear at power and ground pins through the I/Os' coupling path. And the output signals at output pins themselves are sources of conducted emissions to the printed circuit boards.

NOTE The measurement set-up is done according to the IEC 61967 series.

#### **Basic components** 5

#### 5.1 General

The basic components are component parts of the IC macro-model or block component or sub-model component. The following subclauses define the basic components.

NOTE The block component and the sub-model component are defined in Subclause 6.3.1 and 6.4.1 respectively.

#### 5.2 Internal Activity (IA)

The Internal Activity (IA) component is the electromagnetic noise source that originates in switching of active devices in the IC or in a portion of the IC. This component is applicable for both analogue and digital circuitry.

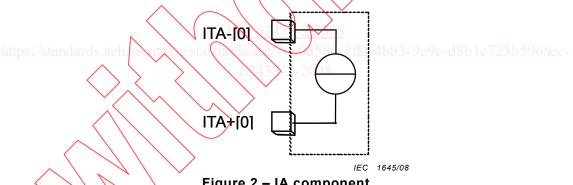

The IA is described using an independent current source or an independent voltage source with two internal terminals as shown in Figure 2.

Figure 2 – IA component

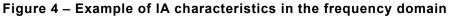

The characteristics of IA component are typically described in the time domain, and the characteristics can also be described in the frequency domain.

The description of an IA component shall contain the following information.

- Name of the IA component

- Names of its internal terminals

- Operational mode or test vector

- Domain (time or frequency)

- Definition of origin of time, and cycle-time for the operational mode (for time domain)

- Definition of origin of phase (for frequency domain)

- Operational conditions and applicable ranges

- a) Power supply voltage ranges

- b) Temperature range

- c) Frequency range

- Characteristics of the IA

- a) Current or voltage waveform over the whole cycle-time (for time domain)

- b) Current or voltage amplitude and phase, versus frequency over the whole frequency range (for frequency domain)

#### EXAMPLE 1

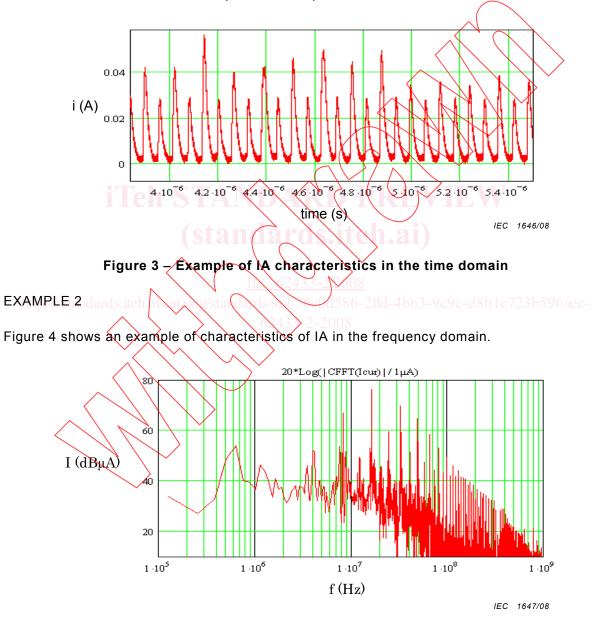

Figure 3 shows an example of characteristics of IA in the time domain. The waveform depends on the specific operational mode of function. A simple waveform such as a triangular waveform can be used for the component description.

#### 5.3 Passive Distribution Network (PDN)

The Passive Distribution Network component (PDN) presents the characteristics of propagation path of electromagnetic noises such as power distribution network (part of the PDN). The PDN can be linear or non-linear.

The PDN consists of passive elements, and is equipped with internal terminals. And the PDN can have external terminals.

The PDN can be described using a netlist. In the case the PDN can be assumed to be linear, some matrix formats such as the S-parameter can also present the PDN characteristics.

The description of a PDN component shall contain the following information.

- Name of the PDN component

- Names of its internal terminals and external terminals

- Applicable ranges

- a) Power supply voltage range

- b) Temperature range

- c) Applicable load conditions if the PDN is for output

- d) Applicable frequency range

- Characteristics of the PDN

#### EXAMPLE 1

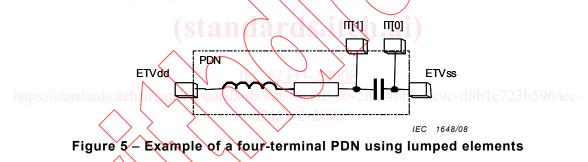

Figure 5 shows an example of a four-terminal PDN using lumped elements. The ETVdd and ETVss are two external terminals of the PDN. The IT[1] and the IT[0] are two internal terminals.

EXAMPLE 2

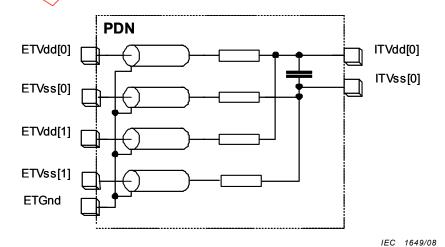

Figure 6 depicts the seven-terminal PDN structure using distributed elements such as transmission lines. The ETVxx are the four external terminals, the ITVxx are two internal terminals and the ETGnd is the common ground of the four transmission lines, connected to the PCB ground.

Figure 6 – Example of a seven-terminal PDN using distributed elements