NOTICE: This standard has either been superseded and replaced by a new version or discontinued. Contact ASTM International (www.astm.org) for the latest information.

An American National Standard

### Standard Guide to Interpretation of Radiographs of Semiconductors and Related Devices<sup>1</sup>

This standard is issued under the fixed designation E 431; the number immediately following the designation indicates the year of original adoption or, in the case of revision, the year of last revision. A number in parentheses indicates the year of last reapproval. A superscript epsilon ( $\epsilon$ ) indicates an editorial change since the last revision or reapproval.

#### 1. Scope

1.1 This guide provides illustrations of radiographs of semiconductors and related devices. Low powered transistors (through the TO-11 case configuration), diodes, low-power rectifiers, power devices, and integrated circuits are illustrated with common assembly features. Particular areas of construction are featured for these devices detailing critical points of design or assembly.

1.2 This standard does not purport to address all of the safety concerns, if any, associated with its use. It is the responsibility of the user of this standard to establish appropriate safety and health practices and determine the applicability of regulatory limitations prior to use.

#### 2. Referenced Documents

- 2.1 ASTM Standards:

- E 801 Practice for Controlling Quality of Radiological Examination of Electronic Devices<sup>2</sup>

- E 1161 Test Method for Radiologic Examination of Semiconductors and Electronic Components<sup>2</sup>

- E 1255 Practice for Radioscopy<sup>2</sup>

- E 1316 Terminology for Nondestructive Examinations<sup>2</sup>AST

- 3. Terminology standards, iten ar catalog/standards/sist/d24

3.1 Definitions of terms used in these reference illustrations may be found in Terminology E 1316, Section D.

#### 4. Significance and Use

4.1 Illustrations provided in this guide are intended for use

as references to aid in interpreting film or nonfilm images resulting from x-ray inspections (see Table 1) to ascertain quality of assembly and workmanship.

4.2 Required attributes of the design features or other construction details are not provided but are to be established as mutually agreed upon by manufacturers and users of these devices. Many devices share common assembly features; thus, these interpretations can be used for components not illustrated.

#### 5. Use of Illustrations

5.1 The illustrations in this guide are for use in interpreting radiographs of semiconductors and related devices. They provide reference points and information on the critical areas of such devices. These points must be clearly resolved in the radiographs being interpreted. The radiographs to be interpreted must comply with the requirements of Practice E 801 to ensure suitable image quality with minimal distortion. Additional information on the application of radiographic techniques to semiconductors and electronic components may be found in Test Method E 1161.

5.2 The illustrations in this guide may also be used to interpret the radioscopic images of semiconductors and related devices when using radioscopic techniques. The radioscopic images to be interpreted must comply with the requirements of Practice E 801 to ensure suitable image quality with minimal distortion. Additional information on the application of radioscopic techniques may be found in Test Method E 1161 and Practice E 1255.

#### 6. Description

6.1 Description of irregularities and applicable figures are shown in Table 1.

#### 7. Keywords

7.1 electronic devices; nondestructive testing; radiographs; radiography; reference illustrations; semiconductors; x-ray

<sup>&</sup>lt;sup>1</sup> This guide is under the jurisdiction of ASTM Committee E-7 on Nondestructive Testing and is the direct responsibility of Subcommittee E07.02 on Reference Radiological Images.

Current edition approved Dec. 10, 1996. Published February 1997. Originally published as E 431 – 71. Last previous edition E 431 – 92.

<sup>&</sup>lt;sup>2</sup> Annual Book of ASTM Standards, Vol 03.03.

# 御 E 431

| TABLE 1 Irregularity Description and Figure Reference | TABLE 1 | Irregularity | Description | and Figure | References |

|-------------------------------------------------------|---------|--------------|-------------|------------|------------|

|-------------------------------------------------------|---------|--------------|-------------|------------|------------|

| Item and Irregularity                                                                      | Expressed as                                                                                                                                                                                                                                                                                                                                |                                  |

|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|                                                                                            | Transistors, low-power (TO-11 and smaller packages)                                                                                                                                                                                                                                                                                         |                                  |

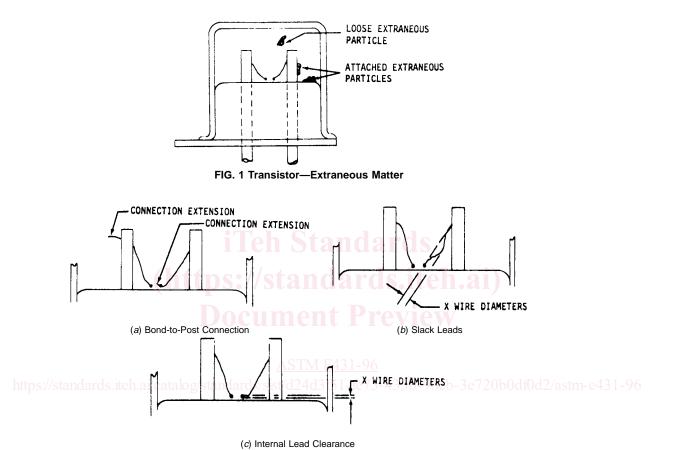

| Extraneous matter                                                                          | Any material contained in the semiconductor device that is not necessary for its manufacture or operation.                                                                                                                                                                                                                                  | 1                                |

| nternal lead irregularities, bond-to-post connection                                       | Leads extending beyond attachment points at either end. Allowable extension should be stated in wire diameters.                                                                                                                                                                                                                             | 2( <i>a</i> )                    |

|                                                                                            | Slack leads deviate from a straight line between attachment points. Allowable deviation should be stated in wire diameters.                                                                                                                                                                                                                 | 2( <i>b</i> )                    |

|                                                                                            | Internal lead clearance is the distance between the edge of the chip and lead wire. Allowable clearance should be stated in wire diameters.                                                                                                                                                                                                 | 2( <i>c</i> )<br>3               |

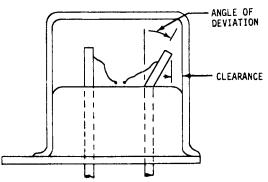

| Post-position irregularities                                                               | Allowable deviations of the post from its intended (design) position may be specified as minimum angle made by the post and header, or as clearance between post and post or post and case expressed in terms of post diameter.                                                                                                             |                                  |

| Getter-position irregularities                                                             | In crimp-type devices, deviations of the getter ring from its intended (design) position are stated relative to the crimp. In noncrimp-type devices, deviations of the getter ring from its intended                                                                                                                                        | 4( <i>a</i> )<br>4( <i>b</i> )   |

| <i>I</i> ounting paste                                                                     | (design) position are stated as the angle between the actual and intended positions.<br>Mounting-paste buildup or expulsion, or both, is an excessive amount of material used to mount<br>the semiconductor element on the header. Allowable excess should be measured relative to                                                          | 5                                |

| Post-connection solder or gold paste                                                       | the surfaces, clearances, and shape of the deposit.<br>Post-connection solder or gold-paste buildup is an excessive amount of such material at the termination. Excess is measured relative to the diameter at the attachment point and by the deposit shape.                                                                               | 6                                |

|                                                                                            | Diodes and low-power rectifiers (whisker-type)                                                                                                                                                                                                                                                                                              |                                  |

| Extraneous matter                                                                          | Any material contained in the cavity of the device that is not part of its design and not required for its manufacture or operation.                                                                                                                                                                                                        | 7( <i>a</i> )<br>7( <i>b</i> )   |

| Vhisker irregularities                                                                     | Any whisker malformation from its intended shape caused by compression. Allowable compression is stated as a percentage of design length.                                                                                                                                                                                                   | 7( <i>c</i> )<br>8( <i>a</i> )   |

|                                                                                            | Whisker cross-sectional-area deviations are stated as a percentage of cross section.                                                                                                                                                                                                                                                        | 8( <i>b</i> )                    |

|                                                                                            | Misalignment irregularities are described by device design and type of construction.<br>Whisker contact to the post or lead is expressed as a percentage of the design contact area.                                                                                                                                                        | none<br>8( <i>c</i> )            |

| Trimped lead devices<br>Trystal and crystal-mounting irregularities                        | Minimum crimp length can be stated.<br>Tilt is the deviation of the mounted crystal from its intended (design) mounting plane. Allowable deviation is expressed in degrees from normal to the main axis of the device.                                                                                                                      | 9<br>10( <i>a</i> )              |

|                                                                                            | Clearance is the distance from the edge of the crystal to the inside wall of the device cavity. It is expressed in units of length (millimeters or inches); if contact is permissible, it should be stated whether or not fusion is allowable.                                                                                              | 10( <i>b</i> )<br>10( <i>c</i> ) |

|                                                                                            | Crystal fusion to the mount is an area of contact between the crystal and the designed mounting surface where fusion occurs. Minimum allowable fusion is stated as a percentage of the design                                                                                                                                               | 10( <i>d</i> )<br>431-96         |

|                                                                                            | <ul> <li>mounting surface.</li> <li>Mounting-paste expulsion is excessive mounting paste. Allowable expulsion is stated as deposit<br/>shape.</li> </ul>                                                                                                                                                                                    | 10( <i>e</i> )                   |

|                                                                                            | Diodes and low-power rectifiers (whiskerless-type)                                                                                                                                                                                                                                                                                          |                                  |

| /lisalignment                                                                              | Crystal position relative to the posts or the posts to one another or both. Allowable crystal misalignment is stated as a percentage of the largest post. Allowable post misalignment is                                                                                                                                                    | 11( <i>a</i> )<br>11( <i>b</i> ) |

| /oids                                                                                      | expressed as a percentage of the diameter of the smallest post.<br>Air bubbles in the encapsulation material used for the semiconductor device. Allowable voids are<br>stated as a percentage of wall thickness and as the distance from the encapsulation ends to<br>the lead seal.                                                        | 12                               |

|                                                                                            | Integrated circuits                                                                                                                                                                                                                                                                                                                         |                                  |

| xtraneous matter                                                                           | Any material contained in the integrated circuit that is not part of its design and not necessary for its manufacture or operation.                                                                                                                                                                                                         | none                             |

| Clearances                                                                                 | Minimum allowable clearances are expressed in units of length (millimeters or inches) or lead-<br>wire diameters. Internal clearances can be stated between parts as: (1) lead to case; (2) lead<br>wire to lead wire; (3) lead wire to bond; (4) lead wire to chip; (5) chip to chip; (6) bond to bond;<br>(7) lead wire to external lead. | 13                               |

| Chip mounting                                                                              | The minimum area of mounting paste used to secure the chip to the header is stated as a percentage of the design contact (chip) area.                                                                                                                                                                                                       | 14( <i>a</i> )                   |

|                                                                                            | Unacceptable configuration of voids should be described.<br>A misaligned chip is one misoriented with respect to its intended position. Misalignment is<br>expressed as an angle or a case-to-chip distance.                                                                                                                                | 14( <i>b</i> )<br>none           |

| founting-paste buildup or expulsion (or both)                                              | An excessive amount of the material used to mount the semiconductor element to the header.<br>Allowable excess is measured relative to the top surface of the semiconductor element and by deposit shape.                                                                                                                                   | 5                                |

| nternal lead irregularities, bond-to-external lead, and pond-to-bond or bond-to-bond leads | Leads extending beyond the attachment points at either end. Allowable extension is stated in wire diameters.                                                                                                                                                                                                                                | none                             |

|                                                                                            | Slack leads deviate from a straight line between the attachment points. Allowable deviation is expressed in wire diameters.                                                                                                                                                                                                                 | none                             |

## 🕼 E 431

TABLE 1

Continued

| Item and Irregularity            | Expressed as                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                  | Power devices (transistors, rectifiers, and silicon-controlled rectifiers)                                                                                                                                                                                                                                                                                                                                               |  |

| Construction methods and designs | Because of the large variety of construction methods and designs, it will generally be necessary to state criteria for each type of device. The usual criteria should include inspection for: (1) extraneous matter; (2) internal clearances; (3) mounting-paste buildup and expulsion; (4) crimp irregularities, where internal leads are crimped into tubular, external leads; (5) internal-connection irregularities. |  |

FIG. 2 Transistor—Internal Lead Irregularities

FIG. 3 Transistor—Post-Position Irregularities