# THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2007 IEEE

All rights reserved. IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of Electrical and Electronics Engineers, Inc.

Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the IEC Central Office. Any questions about IEEE copyright should be addressed to the IEEE. Enquiries about obtaining additional rights to this publication and other information requests should be addressed to the IEC or your local IEC member National Committee.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland Email: inmail@iec.ch Web: www.iec.ch The Institute of Electrical and Electronics Engineers, Inc 3 Park Avenue US-New York, NY10016-5997 USA Email: stds-info@ieee.org Web: www.ieee.org

## About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: www.iec.ch/online\_news/justpub/ Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feetback on this wulliantian or need further assistance, places visit the Customer Service

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us.

Email: csc@iec.ch Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

ICS 25.040

ISBN 2-8318-9352-6

# CONTENTS

| -  |                      | LD                                                                                                |    |  |  |  |  |

|----|----------------------|---------------------------------------------------------------------------------------------------|----|--|--|--|--|

|    |                      | luction                                                                                           |    |  |  |  |  |

| 1. | Overview             |                                                                                                   |    |  |  |  |  |

|    | 1.1                  | Scope                                                                                             |    |  |  |  |  |

|    | 1.2                  | Purpose                                                                                           |    |  |  |  |  |

|    |                      | 1.2.1 Background                                                                                  |    |  |  |  |  |

|    |                      | 1.2.2 Motivation                                                                                  | 9  |  |  |  |  |

|    |                      | 1.2.3 Goals                                                                                       | 9  |  |  |  |  |

|    | 1.3                  | Usage                                                                                             | 9  |  |  |  |  |

|    |                      | 1.3.1 Functional specification                                                                    | 9  |  |  |  |  |

|    |                      | 1.3.2 Functional verification                                                                     | 10 |  |  |  |  |

| 2. | Normative references |                                                                                                   |    |  |  |  |  |

|    | D                    |                                                                                                   |    |  |  |  |  |

| 3. | Def                  | Definitions, acronyms, and abbreviations                                                          |    |  |  |  |  |

|    | 3.1                  | Definitions                                                                                       |    |  |  |  |  |

|    | 3.2                  | Acronyms and abbreviations                                                                        |    |  |  |  |  |

|    | 3.3                  | Special terms                                                                                     |    |  |  |  |  |

|    |                      | $\sim \sim $ |    |  |  |  |  |

| 4. | Org                  | Organization                                                                                      |    |  |  |  |  |

|    | 11                   | Abstract structure                                                                                | 22 |  |  |  |  |

|    | 4.1                  |                                                                                                   |    |  |  |  |  |

|    |                      | 4.1.1 Layers                                                                                      |    |  |  |  |  |

|    | 10                   |                                                                                                   |    |  |  |  |  |

|    | 4.2                  | Lexical structure                                                                                 |    |  |  |  |  |

|    |                      | 4.2.1 Identifiers                                                                                 |    |  |  |  |  |

|    |                      |                                                                                                   |    |  |  |  |  |

|    |                      | 4.2.3 Operators                                                                                   |    |  |  |  |  |

|    |                      | 4.2.4 Macros<br>4.2.5 Comments                                                                    |    |  |  |  |  |

|    | 1 2                  |                                                                                                   |    |  |  |  |  |

|    | 4.3                  | Syntax                                                                                            |    |  |  |  |  |

|    |                      | 4.3.1 Conventions                                                                                 |    |  |  |  |  |

|    | A A                  | 4.3.2 HDL dependencies                                                                            |    |  |  |  |  |

|    |                      | Semantics                                                                                         |    |  |  |  |  |

|    |                      | 4.4.1 Clocked vs unclocked evaluation                                                             |    |  |  |  |  |

|    |                      | 4.4.2 Safety vs. liveness properties                                                              |    |  |  |  |  |

|    |                      | 4.4.3 Linear vs. branching logic                                                                  |    |  |  |  |  |

|    |                      | 4.4.4 Simple subset                                                                               |    |  |  |  |  |

|    |                      | 4.4.5 Finite-length vs. infinite-length behavior                                                  |    |  |  |  |  |

|    |                      | 4.4.6 The concept of strength                                                                     |    |  |  |  |  |

| 5. | Boo                  | Boolean layer                                                                                     |    |  |  |  |  |

|    | 5.1                  | Expression type classes                                                                           | 40 |  |  |  |  |

|    |                      | 5.1.1 Bit expressions                                                                             |    |  |  |  |  |

|    |                      | 5.1.2 Boolean expressions                                                                         |    |  |  |  |  |

|    |                      | 5.1.3 BitVector expressions                                                                       |    |  |  |  |  |

|    |                      | 5.1.4 Numeric expressions                                                                         |    |  |  |  |  |

|    |                      | 5.1.5 String expressions                                                                          |    |  |  |  |  |

|    | 5.2                  | Expression forms                                                                                  |    |  |  |  |  |

|    | 5.2                  | 5.2.1 HDL expressions                                                                             |    |  |  |  |  |

|       | 5.2.2 PSL expressions                                          | 45  |

|-------|----------------------------------------------------------------|-----|

|       | 5.2.3 Built-in functions                                       |     |

|       | 5.2.4 Union expressions                                        |     |

|       | 5.3 Clock expressions                                          |     |

|       | 5.4 Default clock declaration                                  |     |

| 6.    | Temporal layer                                                 | 56  |

|       | 6.1 Sequential expressions                                     | 57  |

|       | 6.1.1 Sequential Extended Regular Expressions (SEREs)          | 57  |

|       | 6.1.2 Sequences                                                | 64  |

|       | 6.2 Properties                                                 | 70  |

|       | 6.2.1 FL properties                                            | 71  |

|       | 6.2.2 Optional Branching Extension (OBE) properties            | 91  |

|       | 6.2.3 Replicated properties                                    | 98  |

|       | 6.3 Property and sequence declarations                         | 100 |

|       | 6.3.1 Parameters                                               |     |

|       | 6.3.2 Declarations                                             | 103 |

|       | 6.3.3 Instantiation                                            |     |

|       |                                                                |     |

| 7.    | Verification layer                                             | 108 |

|       | 7.1 Verification directives                                    | 108 |

|       | 7.1.1 assert                                                   | 108 |

|       | 7.1.2 assume                                                   |     |

|       | 7.1.2 assume_guarantee                                         |     |

|       | 7.1.4 restrict                                                 |     |

|       | 7.1.5 restrict_guarantee                                       |     |

|       | 7.1.6 cover                                                    | 111 |

|       | 7.1.7 fairness and strong_fairness                             | 112 |

|       | 7.1 Verification units                                         | 112 |

|       | 7.2.1 Verification unit binding                                | 115 |

|       | ards 7.2.2 Verification unit inheritance                       |     |

|       | 7.2.3 Verification unit scoping rules                          |     |

|       | 7.2.5 Vernication unit scoping rules                           | 117 |

| 8.    | Modeling layer                                                 | 120 |

| 0.    | Would high Reven                                               | 120 |

|       | Q 1 Interior tengos                                            | 120 |

|       | 8.1 Integer ranges<br>8.2 Structures                           | 120 |

| 1     | a.2 Structures                                                 |     |

|       |                                                                |     |

| Anney | B (normative) Formal syntax and semantics of IEEE Std 1850 PSL | 136 |

| Annex | C (informative) Bibliography                                   | 146 |

| Anney | D (informative) List of participants                           | 148 |

|       |                                                                |     |

| Index |                                                                | 150 |

|       |                                                                |     |

## INTERNATIONAL ELECTROTECHNICAL COMMISSION

# STANDARD FOR PROPERTY SPECIFICATION LANGUAGE (PSL)

# FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes (International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for dentifying any or all such patent rights.

#### https://standards.iteh.ai

International Standard IEC/IEEE 62531 has been processed through Technical Committee 93: Design automation.

The text of this standard is based on the following documents:

| IEEE Std   | FDIS        | Report on voting |

|------------|-------------|------------------|

| 1850(2005) | 93/253/FDIS | 93/264/RVD       |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

#### **IEC/IEEE Dual Logo International Standards**

This Dual Logo International Standard is the result of an agreement between the IEC and the Institute of Electrical and Electronics Engineers, Inc. (IEEE). The original IEEE Standard was submitted to the IEC for consideration under the agreement, and the resulting IEC/IEEE Dual Logo International Standard has been published in accordance with the ISO/IEC Directives.

IEEE Standards documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and serve without compensation. While the IEEE administers the process and establishes rules to promote fairness in the consensus development process, the IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Use of an IEC/IEEE Dual Logo International Standard is wholly voluntary. The IEC and IEEE disclaim liability for any personal injury, property or other damage, of any nature whatsoever, whether special, indirect, consequential, or compensatory, directly or indirectly resulting from the publication, use of, or reliance upon this, or any other IEC or IEEE Standard document.

The IEC and IEEE do not warrant or represent the accuracy or content of the material contained herein, and expressly disclaim any express or implied warranty, including any implied warranty of merchantability or fitness for a specific purpose, or that the use of the material contained herein is free from patent infringement. IEC/IEEE Dual Logo International Standards documents are supplied "AS IS".

The existence of an IEC/IEEE Dual Logo International Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEC/IEEE Dual Logo International Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

In publishing and making this document available, the IEC and IEEE are not suggesting or rendering professional or other services for, or on behalf of, any person or entity. Neither the IEC nor IEEE is undertaking to perform any duty owed by any other person or entity to another. Any person utilizing this, and any other IEC/IEEE Dual Logo International Standards or IEEE Standards document, should rely upon the advice of a competent professional in determining the exercise of reasonable care in any given circumstances.

Interpretations – Occasional questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of

nttps interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are on the analysis of the provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments for revision of IEC/IEEE Dual Logo International Standards are welcome from any interested party, regardless of membership affiliation with the IEC or IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE-SA Standards Board, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA and/or General Secretary, IEC, 3, rue de Varembé, PO Box 131, 1211 Geneva 20, Switzerland.

Authorization to photocopy portions of any individual standard for internal or personal use is granted by the Institute of Electrical and Electronics Engineers, Inc., provided that the appropriate fee is paid to Copyright Clearance Center. To arrange for payment of licensing fee, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

NOTE – Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying patents for which a license may be required by an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention.

# **IEEE Standard for**

# Property Specification Language (PSL)

Sponsor

Design Automation Standards Committee of the IEEE Computer Society

and the IEEE Standards Association Corporate Advisory Group

Approved 22 September 2005

**IEEE-SA Standards Board**

Grateful acknowledgment is made to Accellera Organization, Inc. for the permission to use the following source material:

-6-

Accellera Property Specification Language Reference Manual (version 1.1), Accellera

GDL: General Description Language, Accellera, Mar. 2005

https://standards.iteh.ai

**Abstract:** The IEEE Property Specification Language (PSL) is defined in this standard. PSL is a formal notation for specification of electronic system behavior, compatible with multiple electronic system design languages, including IEEE Std 1076<sup>™</sup> (VHDL<sup>®</sup>), IEEE Std 1364<sup>™</sup> (Verilog<sup>®</sup>), IEEE P1666<sup>™</sup> (SystemC<sup>®</sup>), and IEEE P1800<sup>™</sup> (SystemVerilog<sup>®</sup>), thereby enabling a common specification and verification flow for multi-language and mixed-language designs. PSL captures design intent in a form suitable for simulation, formal verification, formal analysis, and hybrid verification tools. PSL enhances communication among architects, designers, and verification engineers to increase productivity throughout the design and verification process. The primary audiences for this standard are the implementors of tools supporting the language and advanced users of the language.

**Keywords:** ABV, assertion, assertion-based verification, assumption, cover, model checking, property, PSL, specification, temporal logic, verification

IEEE Std 1850 Property Specification Language (PSL) is based upon the Accellera Property Specification Language (Accellera PSL), a language for formal specification of electronic system behavior, which was developed by Accellera, a consortium of Electronic Design Automation (EDA), semiconductor, and system companies. IEEE Std 1850 PSL refines Accellera PSL version 1.1, addressing errata and a few minor technical issues and clarifying how PSL interfaces with various standard electronic system design languages.

# Notice to users

## Errata

Errata, if any, for this and all other standards can be accessed at the following URL: <u>http://</u><u>standards.ieee.org/reading/ieee/updates/errata/index.html.</u> Users are encouraged to check this URL for errata periodically.

# Interpretations

Current interpretations can be accessed at the following URL: http://standards.ieee.org/reading/ieee/interp/ index.html.

## Patents

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken with respect to the existence or validity of any patent rights in connection therewith. The IEEE shall not be responsible for identifying patents or patent applications for which a license may be required to implement an IEEE standard or for conducting inquiries into the legal validity or scope of those patents that are brought to its attention. A patent holder or patent applicant has filed a statement of assurance that it will grant licenses under these rights without compensation or under reasonable rates and nondiscriminatory, reasonable terms and conditions to applicants destring to obtain such licenses. The IEEE makes no representation as to the reasonableness of rates, terms, and conditions of the license agreements offered by patent holders or patent applicants. Further information may be obtained from the IEEE Standards Department.

# STANDARD FOR PROPERTY SPECIFICATION VOLTAGE (PSL)

# 1. Overview

#### 1.1 Scope

This standard defines the property specification language (PSL), which formally describes electronic system behavior. This standard specifies the syntax and semantics for PSL and also clarifies how PSL interfaces with various standard electronic system design languages.

- 8 -

#### 1.2 Purpose

The purpose of this standard is to provide a well-defined language for formal specification of electronic system behavior, one that is compatible with multiple electronic system design languages, including IEEE Std 1076<sup>TM</sup> (VHDL), IEEE Std 1364<sup>TM</sup> (Verilog<sup>®</sup>), IEEE P1800<sup>TM1</sup> (SystemVerilog<sup>®</sup>), and IEEE P1666<sup>TM</sup> (SystemC), to facilitate a common specification and verification flow for multi-language and mixed-language designs.

#### 1.2.1 Background

The complexity of Very Large Scale Integration (VLSI) has grown to such a degree that traditional approaches have begun to reach their limitations, and verification costs have reached 60%–70% of development resources. The need for advanced verification methodology, with improved observability of design behavior and improved controllability of the verification process, has become critical. Over the last decade, a methodology based on the notion of "properties" has been identified as a powerful verification paradigm that can assure enhanced productivity, higher design quality and, ultimately, faster time to market and higher value to engineers and end-users of electronics products. Properties, as used in this context, are concise, declarative, expressive and unambiguous specifications of desired system behavior, that are used to guide the verification process. IEEE Std 1850 PSL is a standard language for specifying electronic system behavior using properties. PSL facilitates property-based verification using both simulation and formal verification, thereby enabling a productivity boost in functional verification.

<sup>&</sup>lt;sup>1</sup>Numbers preceded by P are IEEE authorized standards projects that were not approved by the IEEE-SA Standards Board at the time this publication went to press. For information about obtaining drafts, contact the Institute of Electrical and Electronics Engineers, Inc.

#### 1.2.2 Motivation

Ensuring that a design's implementation satisfies its specification is the foundation of hardware verification. Key to the design and verification process is the act of specification. Yet historically, the process of specification has consisted of creating a natural language description of a set of design requirements. This form of specification is both ambiguous and, in many cases, unverifiable due to the lack of a standard machine-executable representation. Furthermore, ensuring that all functional aspects of the specification have been adequately *verified* (that is, covered) is problematic.

The IEEE PSL was developed to address these shortcomings. It gives the design architect a standard means of specifying design properties using a concise syntax with clearly-defined formal semantics. Similarly, it enables the RTL implementer to capture design intent in a verifiable form, while enabling the verification engineer to validate that the implementation satisfies its specification through *dynamic* (that is, simulation) and *static* (that is, formal) verification means. Furthermore, it provides a means to measure the quality of the verification process through the creation of functional coverage models built on formally specified properties. In addition, it provides a standard means for hardware designers and verification engineers to create a rigorous and machine-executable design specification.

#### 1.2.3 Goals

PSL was specifically developed to fulfill the following general hardware functional specification requirements:

- Easy to learn, write, and read

- Concise syntax

- Rigorously well-defined formal semantics

- Expressive power, permitting specifications of a large class of real-world design properties

- Known efficient underlying algorithms in simulation, as well as formal verification

#### 1.3 Usage

PSL is a language for the formal specification of hardware. It is used to describe properties that are required to hold in the design under verification. PSL provides a means to write specifications that are both easy to read and mathematically precise. It is intended to be used for functional specification on the one hand and as input to functional verification tools on the other. Thus, a PSL specification is an executable specification of a hardware design.

# 1.3.1 Functional specification

PSL can be used to capture requirements regarding the overall behavior of a design, as well as assumptions about the environment in which the design is expected to operate. PSL can also capture internal behavioral requirements and assumptions that arise during the design process. Both enable more effective functional verification and reuse of the design.

One important use of PSL is for documentation, either in place of or along with an English specification. A PSL specification can describe simple invariants (for example, signals read\_enable and write\_enable are never asserted simultaneously) as well as multi-cycle behavior (for example, correct behavior of an interface with respect to a bus protocol or correct behavior of pipelined operations).

A PSL specification consists of *assertions* regarding *properties* of a design under a set of *assumptions*. A *property* is built from three kinds of elements: *Boolean expressions*, which describe behavior over one cycle; *sequential expressions*, which can describe multi-cycle behavior; and *temporal operators*, which describe

temporal relationships among Boolean expressions and sequences. For example, consider the following Verilog Boolean expression:

ena || enb

This expression describes a cycle in which at least one of the signals ena and enb are asserted. The PSL sequential expression

{req; ack; !cancel}

describes a sequence of cycles, such that req is asserted in the first cycle, ack is asserted in the second cycle, and cancel is deasserted in the third cycle. The following property, obtained by applying the temporal operators always and |=> to these expressions,

```

always {req;ack;!cancel} |=> (ena || enb)

```

means that always (that is, in every cycle), if the sequence {req;ack; cancel} occurs, then either ena or enb is asserted one cycle after the sequence ends. Adding the directive assert as follows:

enb)

assert always {req;ack;!cancel} |=> (enal

completes the specification, indicating that this property is expected to hold in the design and that this expectation needs to be verified.

## 1.3.2 Functional verification

PSL can also be used as input to verification tools, for both verification by simulation, as well as formal verification using a model checker or a theorem prover. Each of these is discussed in the subclauses that follow.

#### 1.3.2.1 Simulation

https:/ A PSL specification can also be used to automatically generate checks of simulated behavior. This can be [-2007] done, for example, by directly integrating the checks in the simulation tool; by interpreting PSL properties in a testbench automation tool that drives the simulator; by generating HDL monitors that are simulated alongside the design; or by analyzing the traces produced during simulation.

For instance, the following PSL property:

```

Property 1: always (req -> next !req)

```

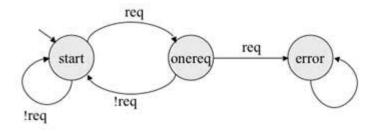

states that signal req is a pulsed signal, i.e., if it is high in some cycle, then it is low in the following cycle. Such a property can be easily checked using a simulation checker written in some HDL that has the functionality of the finite state machine (FSM) shown in Figure 1.

Figure 1—A simple (deterministic) FSM that checks Property 1

For properties more complicated than the property shown in Figure 1, manually writing a corresponding checker is painstaking and error-prone, and maintaining a collection of such checkers for a constantly changing design under development is a time-consuming task. Instead, a PSL specification can be used as input to a tool that automatically generates simulatable checkers.

Although in principle, all PSL properties can be checked for finite paths in simulation, the implementation of the checks is often significantly simpler for a subset called the *simple subset* of PSL. Informally, in this subset, composition of temporal properties is restricted to ensure that time *moves forward* from left to right through a property, as it does in a timing diagram. (See 4.4.4 for the formal definition of the simple subset.) For example, the property

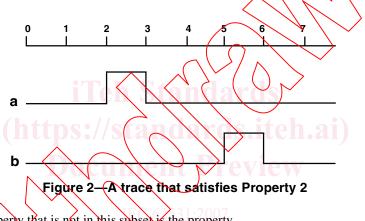

Property 2: always (a -> next[3] b)

which states that, if a is asserted, then b is asserted three cycles later, belongs to the simple subset, because a appears to the left of b in the property and also appears to the left of b in the timing diagram of any behavior that is not a violation of the property. Figure 2 shows an example of such a timing diagram.

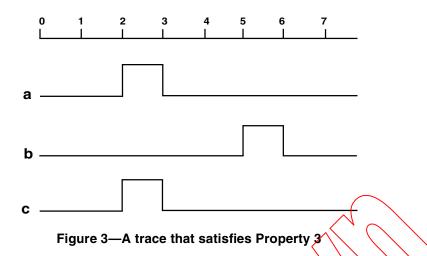

An example of a property that is not in this subset is the property Property 3: always (\a && next [3] b) -> c)

which states that, if a is asserted and b is asserted three cycles later, then c is asserted (in the same cycle as a). This property does not belong to the simple subset, because although c appears to the right of a and b in the property, it appears to the left of b in a timing diagram that is not a violation of the property. Figure 3 shows an example of such a timing diagram.

#### 1.3.2.2 Formal verification

PSL is an extension of the standard temporal logics Linear-Time Temporal Logic (LTL) and Computation Tree Logic (CTL). A specification in the PSL Foundation Language (respectively, the PSL Optional Branching Extension) can be *compiled down* to a formula of pure LTL (respectively, CTL), possibly with some auxiliary HDL code, known as a *satellite*.

https://standards.iteh.

c5-fe93-4950-aa5a-1c34d73a5e9c/iec-62531-2007