Edition 2.0 2011-04

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

## Semiconductor devices – Mechanical and climatic test methods – Part 29: Latch-up test (standards.iteh.ai)

Dispositifs à semiconducteurs – <u>Méthodes d'essai mécaniques et climatiques</u> – Partie 29: Essai de verrouillage atalog/standards/sist/cc15bf7e-f425-4571-b783-386be25fl 837/jec-60749-29-2011

### THIS PUBLICATION IS COPYRIGHT PROTECTED

#### Copyright © 2011 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur. Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office 3, rue de Varembé CH-1211 Geneva 20 Switzerland Email: inmail@iec.ch Web: www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

Catalogue of IEC publications: www.iec.ch/searchpub ARD PREVIEW

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, withdrawn and replaced publications.

IEC Just Published: www.iec.ch/online news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available on-line and also by email.

• Electropedia: <u>www.electropedia.otg/ds.itch.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783-</u> The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical Vocabulary online.

Customer Service Centre: <u>www.iec.ch/webstore/custserv</u>

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service Centre FAQ or contact us:

Email: <u>csc@iec.ch</u> Tel.: +41 22 919 02 11 Fax: +41 22 919 03 00

#### A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

#### A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez l'édition la plus récente, un corrigendum ou amendement peut avoir été publié.

Catalogue des publications de la CEI: <u>www.iec.ch/searchpub/cur\_fut-f.htm</u>

Le Catalogue en-ligne de la CEI vous permet d'effectuer des recherches en utilisant différents critères (numéro de référence, texte, comité d'études,...). Il donne aussi des informations sur les projets et les publications retirées ou remplacées.

Just Published CEI: <u>www.iec.ch/online\_news/justpub</u>

Restez informé sur les nouvelles publications de la CEI. Just Published détaille deux fois par mois les nouvelles publications parues. Disponible en-ligne et aussi par email.

Electropedia: <u>www.electropedia.org</u>

Le premier dictionnaire en ligne au monde de termes électroniques et électriques. Il contient plus de 20 000 termes et définitions en anglais et en français, ainsi que les termes équivalents dans les langues additionnelles. Egalement appelé Vocabulaire Electrotechnique International en ligne.

Service Clients: <u>www.iec.ch/webstore/custserv/custserv\_entry-f.htm</u>

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions, visitez le FAQ du Service clients ou contactez-nous:

Email: <u>csc@iec.ch</u> Tél.: +41 22 919 02 11

Fax: +41 22 919 03 00

Edition 2.0 2011-04

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

## Semiconductor devices – Mechanical and climatic test methods – Part 29: Latch-up test (standards.iteh.ai)

Dispositifs à semiconducteurs – <u>Méthodes</u> d'essai mécaniques et climatiques – Partie 29: Essai de verrouillage atalog/standards/sist/cc15bf7e-f425-4571-b783-386be25f1837/iec-60749-29-2011

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

PRICE CODE CODE PRIX

Т

ICS 31.080.01

ISBN 978-2-88912-434-3

### CONTENTS

| FO                                              | REWC          | DRD       |                                                                                                                     | 3  |  |  |

|-------------------------------------------------|---------------|-----------|---------------------------------------------------------------------------------------------------------------------|----|--|--|

| 1                                               | Scop          | e and ol  | oject                                                                                                               | 5  |  |  |

| 2                                               | Term          | s and de  | efinitions                                                                                                          | 5  |  |  |

| 3                                               | Class         | ificatior | and levels                                                                                                          | 8  |  |  |

|                                                 | 3.1           | Classif   | ication                                                                                                             | 8  |  |  |

|                                                 | 3.2           | Levels    |                                                                                                                     | 8  |  |  |

| 4                                               | Арра          | ratus ar  | nd material                                                                                                         | 8  |  |  |

|                                                 | 4.1           | Latch-u   | ıp tester                                                                                                           | 8  |  |  |

|                                                 |               | 4.1.1     | General                                                                                                             | 8  |  |  |

|                                                 |               | 4.1.2     | V <sub>supply</sub> and their qualification method                                                                  | 9  |  |  |

|                                                 |               | 4.1.3     | Trigger source qualification method                                                                                 |    |  |  |

|                                                 | 4.2           |           | ated test equipment (ATE)                                                                                           |    |  |  |

|                                                 | 4.3           |           | purce                                                                                                               |    |  |  |

| 5                                               | Proce         |           |                                                                                                                     |    |  |  |

|                                                 | 5.1           | Genera    | Il latch-up test procedure                                                                                          | 10 |  |  |

|                                                 | 5.2           | Detaile   | d latch-up test procedure                                                                                           |    |  |  |

|                                                 |               | 5.2.1     | I-test                                                                                                              |    |  |  |

|                                                 |               | 5.2.2     | V <sub>supply</sub> overvoltage testA.R.DP.R.E.V.I.R.                                                               | 17 |  |  |

|                                                 |               | 5.2.3     | Testing dynamic devices<br>DUT dispositionstandards.iteh.ai)                                                        | 19 |  |  |

|                                                 |               | 5.2.4     | DUT disposition Lanuar us. (LCII. a)                                                                                | 19 |  |  |

|                                                 |               | 5.2.5     | Record keeping<br>IFC 60749-29/2011                                                                                 | 19 |  |  |

| 6                                               | Failu         | re criter | Record keeping<br>ia IEC 60749-29:2011<br>https://standards.iteh.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783- | 20 |  |  |

| 7                                               | Sumr          | nary      |                                                                                                                     | 20 |  |  |

|                                                 |               |           | tive) Examples of special pins that are connected to passive                                                        | 21 |  |  |

|                                                 |               |           | tive) Calculation of operating ambient or operating case temperature ting junction temperature                      | 23 |  |  |

|                                                 |               |           |                                                                                                                     |    |  |  |

|                                                 |               |           | , qualification circuit                                                                                             |    |  |  |

| Figure 2 – Trigger source qualification circuit |               |           |                                                                                                                     |    |  |  |

| Figure 3 – Latch-up test flow                   |               |           |                                                                                                                     |    |  |  |

| Figu                                            | ure 4 -       | – Test w  | vaveform for positive I-test                                                                                        | 14 |  |  |

| Figure 5 – Test waveform for negative I-test    |               |           |                                                                                                                     |    |  |  |

|                                                 |               |           | alent circuit for positive input/output I-test latch-up testing                                                     |    |  |  |

| Figu                                            | ure 7 -       | – Equiva  | alent circuit for negative input/output I-test latch-up testing                                                     | 17 |  |  |

| -                                               |               |           | vaveform for V <sub>supply</sub> overvoltage                                                                        |    |  |  |

|                                                 |               |           | alent circuit for V <sub>supply</sub> overvoltage test latch-up testing                                             |    |  |  |

|                                                 |               |           | mples of special pins that are connected to passive components                                                      |    |  |  |

| igu                                             | ло <b>д</b> . |           |                                                                                                                     |    |  |  |

|                                                 |               |           | atrix <sup>a</sup>                                                                                                  |    |  |  |

| Tab                                             | le 2 –        | Timing    | specifications for I-test and $V_{supply}$ overvoltage test                                                         | 13 |  |  |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### SEMICONDUCTOR DEVICES – MECHANICAL AND CLIMATIC TEST METHODS –

#### Part 29: Latch-up test

#### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-29 has been prepared by IEC technical committee 47: Semiconductor devices.

This second edition cancels and replaces the first edition published in 2003 and constitutes a technical revision. The significant changes with respect to the previous edition include:

- a number of minor technical changes;

- the addition of two new annexes covering the testing of special pins and temperature calculations.

The text of this standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 47/2083/FDIS | 47/2090/RVD      |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 60749 series, under the general title *Semiconductor devices* – *Mechanical and climatic test methods*, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

# iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>IEC 60749-29:2011</u> https://standards.iteh.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783-386be25f1837/iec-60749-29-2011

### SEMICONDUCTOR DEVICES – MECHANICAL AND CLIMATIC TEST METHODS –

#### Part 29: Latch-up test

#### **1** Scope and object

This part of IEC 60749 covers the I-test and the overvoltage latch-up testing of integrated circuits.

This test is classified as destructive.

The purpose of this test is to establish a method for determining integrated circuit (IC) latchup characteristics and to define latch-up failure criteria. Latch-up characteristics are used in determining product reliability and minimizing "no trouble found" (NTF) and "electrical overstress" (EOS) failures due to latch-up.

This test method is primarily applicable to CMOS devices. Applicability to other technologies must be established.

The classification of latch-up as a function of temperature is defined in 3.1 and the failure level criteria are defined in 3.2 (standards.iteh.ai)

#### 2 Terms and definitions

IEC 60749-29:2011

https://standards.iteh.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783-

For the purposes of this document, the following terms and definitions apply.

#### 2.1

#### cool-down time

period of time between successive applications of trigger pulses or the period of time between the removal of the  $V_{supply}$  voltage and the application of the next trigger pulse (See Figures 4, 5, and 8 and Table 2.)

#### 2.2

### device under test

**DUT** semiconductor product subjected to latch-up test

#### 2.3

ground

GND

common or zero-potential pin(s) of the DUT

NOTE 1 Ground pins are not latch-up tested.

NOTE 2 A ground pin is sometimes called  $V_{ss}$ .

#### 2.4

#### input pins

all address, data-in control, V<sub>ref</sub> and similar pins

#### 2.5

#### I/O (bi-directional) pins

device pins that can be made to operate as an input or output or in a high-impedance state

#### 2.6

$I_{supply}$  total supply current in each  $V_{supply}$  pin (or pin group) with the DUT biased as indicated in Table 1

#### 2.7

I-test

latch-up test that supplies positive and negative current pulses to the pin under test

#### 2.8

#### latch-up

state in which a low-impedance path resulting from an overstress that triggers a parasitic thyristor structure, persists after removal or cessation of the triggering condition

NOTE 1 The overstress can be a voltage or current surge, an excessive rate of change of current or voltage, or any other abnormal condition that causes the parasitic thyristor structure to become regenerative.

NOTE 2 Latch-up will not damage the device provided that the current through the low-impedance path is sufficiently limited in magnitude or duration.

#### 2.9

#### logic-high

level within the more positive (less negative) of the two ranges of logic levels chosen to represent the logic states

NOTE 1 For digital devices, a voltage level equal to N<sub>supply</sub> is used for latch-up testing, except where otherwise specified in the relevant specification.

NOTE 2 For non-digital devices, V<sub>supply</sub> voltage level or the maximum operating voltage that can be applied to that pin as defined in the relevant specification may be used for latch-up testing.

#### 2.10

#### IEC 60749-29:2011 https://standards.iteh.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783-

logic-low level within the more negative (less positive) of the two ranges of logic levels chosen to represent the logic states

NOTE 1 For digital devices, ground voltage level is used for latch-up testing, except where specified in the relevant specification.

NOTE 2 For non-digital devices, ground voltage level or the minimum operating voltage that can be applied to that pin as defined in the relevant specification may be used for latch-up testing.

#### 2.11

## maximum V<sub>supply</sub>

maximum operating voltage for operation within performance specifications

NOTE 1 The maximum voltage is not the absolute maximum voltage beyond which permanent damage is likely.

NOTE 2 Maximum refers to the magnitude of V<sub>supply</sub> and can be either positive or negative.

#### 2.12

#### no connect pin

pin that has no internal connection and that can be used as a support for external wiring without disturbing the function of the device

NOTE All "no connect" pins should be left in an open (floating) state during latch-up testing.

#### 2.13

**nominal**  $I_{supply}$  ( $I_{nom}$ ) measured dc supply current for each  $V_{supply}$  pin (or pin group) with the DUT biased at the test temperature as defined in Clause 5 and Table 1

#### 2.14

#### output pin

device pin that generates a signal or voltage level as a normal function during the normal operation of the device

NOTE Output pins, though left in an open (floating) state during testing of other pin types, are latch-up tested.

#### 2.15

#### preconditioned pin

device pin that has been placed in a defined state or condition (input, output, high impedance, etc.) by applying control vectors to the DUT

#### 2.16

#### testing of dynamic devices

latch-up trigger testing of a device in a known stable state, at the minimum-rated clock frequency applied to the device (see 5.2.3 for specified conditions)

#### 2.17

#### test condition

test temperature, supply voltage, current limits, voltage limits, clock frequency, input bias voltages, and preconditioning vectors applied to the DUT during the latch-up test

#### 2.18

#### timing-related input pin

pin such as clock crystal oscillator, charge pump circuit, etc., required to place the DUT in a normal operating mode

### (standards.iteh.ai)

NOTE Required timing signals may be applied by the latch-up tester, external equipment, and/or external components as appropriate.

#### IEC 60749-29:2011

#### https://standards.iteh.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783-

#### trigger pulse

#### 386be25f1837/iec-60749-29-2011

positive or negative current pulse (I-Test) or voltage pulse ( $V_{supply}$  overvoltage test) applied to any pin under test in an attempt to induce latch-up (see Figures 4, 5 and 8)

#### 2.20

2.19

#### trigger duration

duration of an applied pulse from the trigger source (see Figures 4, 5 and 8 and Table 2)

#### 2.21

$V_{\text{supply}}$  pin (or pin group) all DUT power supply and external voltage source pins (excluding ground pins), including both positive- and negative-potential pins

NOTE 1 Generally, it is permissible to treat equal potential voltage source pins as one V<sub>supply</sub> pin (or pin group) and connect them to one power supply.

NOTE 2 When forming  $V_{supply}$  pins (or pin groups), the combination of  $V_{supply}$  pins with significantly different supply current levels is not recommended as this would make it difficult to detect significant current changes on low supply current pins.

#### 2.22

#### V<sub>supply</sub> overvoltage test

latch-up test that supplies overvoltage pulses or overvoltage d.c. level to the  $V_{supply}$  pin under test

#### 2.23

### V<sub>supply</sub> voltage level

applicable voltage level of the  $V_{supply}$  pin specified in the relevant specification. The  $V_{supply}$ voltage level is used for latch-up testing as the typical logic high level unless otherwise specified (see 2.9)

#### 2.24

#### ground voltage level

ground potential used for latch-up testing as the typical logic low level, unless otherwise specified (see 2.10)

#### 3 Classification and levels

#### 3.1 Classification

There are two classes for latch-up testing.

- Class I is for testing at room temperature ambient.

- Class II is for testing at the maximum operating ambient temperature  $(T_a)$  or maximum operating case temperature  $(T_c)$  or maximum operating junction temperature  $(T_j)$  in the detailed specification.

For Class II testing at the maximum operating  $T_a$  or  $T_c$ , the ambient temperature or case temperature ( $T_c$ ) shall be established at the required test value. For Class II testing at the maximum operating  $T_j$ , the ambient temperature  $T_a$  or the case temperature  $T_c$  should be selected to achieve a temperature characteristic of the junction temperature for a given device operating mode(s) during latch-up testing. The maximum operating ambient or case temperature during stress may be calculated based on the methods detailed in Annex B.

NOTE Elevated temperature will reduce latch-up resistance, and class II testing is recommended for devices that are required to operate at elevated temperature.

#### 3.2 Levels

# (standards.iteh.ai)

Level defines the I-test current injection value used during latch-up testing. Latch-up passing levels are defined as follows: <u>IEC 60749-29:2011</u>

https://standards.iteh.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783-

Level A – The trigger current value in Table 1 shall be +100 mA as defined in Figure 6 and -100 mA as defined in Figure 7. If all pins on the part pass at least the Level A trigger current values, then the part shall be considered a Level A part.

Level B – If any pins on the part do not pass the Level A standard, then the supplier shall determine the minimum passing trigger current requirement for each pin stressed differently than in Level A. The maximum (or highest) passing trigger current value shall be reported in the record for each pin stressed differently than in Level A, and the part shall be considered to be a Level B part, see 5.2.5.

#### 4 Apparatus and material

The apparatus required for this test method includes the following.

#### 4.1 Latch-up tester

#### 4.1.1 General

Test equipment capable of performing the tests as specified in this standard. For devices requiring dynamic testing, the test equipment shall be capable of supplying timing signals and logic setup vectors required to control the I/O pin output states as specified in 5.2.3. The required timing signals and logic vectors may be applied by the latch-up tester itself, external equipment, and/or external components as appropriate.

#### 4.1.2 V<sub>supply</sub> and their qualification method

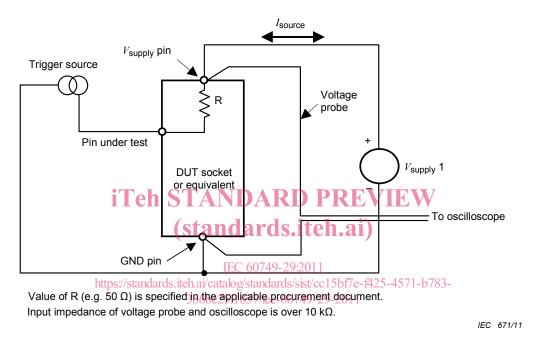

For the I-test, sink type voltage power supplies shall be connected to all  $V_{supply}$  pins as shown in Figure 6 and Figure 7, and the transient characteristics shall be qualified as shown in Figure 1. The qualification steps are as follows:

- a) Connect the supply voltage (e.g. 5 V, 3,3 V) to the  $V_{supply}$  pin. The value of voltage may be specified in the relevant specification.

- b) Apply positive and negative pulses from the 200 mA trigger source, and measure their effect on the voltage waveform shown on the oscilloscope.

- c) The voltage measured by the oscilloscope shall be within 90 % to 110 % of the supply voltage.

Figure 1 –  $V_{supply}$  qualification circuit

#### 4.1.3 Trigger source qualification method

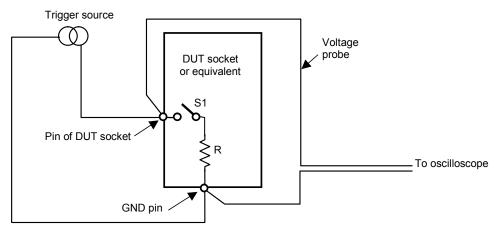

The electrical characteristics of the trigger source including its transient characteristics shall be qualified as shown in Figure 2. The qualification steps are as follows:

- a) With switch S1 closed, apply positive and negative pulses from the 200 mA trigger source, and measure its current waveform. The current waveform shall satisfy the requirements of Table 1.

- b) After setting the voltage clamp level and opening S1, apply positive and negative pulses from the 100 mA trigger source and measure its voltage waveform. The voltage waveform during the working voltage clamp shall be within 90 % to 110 % of the voltage clamp setting level.

Value of R (e.g. 50  $\Omega$ ) is specified in the applicable specification. Input impedance of voltage probe and oscilloscope is over 10 k $\Omega$ .

IEC 672/11

#### Figure 2 – Trigger source qualification circuit

#### 4.2 Automated test equipment (ATE)

A device tester capable of performing full functional and parametric testing of the device specified in the relevant specification. NDARD PREVIEW

#### 4.3 Heat source

# (standards.iteh.ai)

Equipment capable of heating and maintaining the DUT at the maximum operating temperature specified in the relevant specification?during the latch-up test.

https://standards.iteh.ai/catalog/standards/sist/cc15bf7e-f425-4571-b783-386be25f1837/iec-60749-29-2011

#### 5 Procedure

#### 5.1 General latch-up test procedure

Prior to the latch-up test, the device needs to be in a stable state with reproducible  $I_{nom}$ . Engineering judgment may be needed to achieve sufficient stability. The supply current should be made as low as practicable. The supply current must be stable enough and low enough to reliably detect the supply current increase if latch-up occurs.

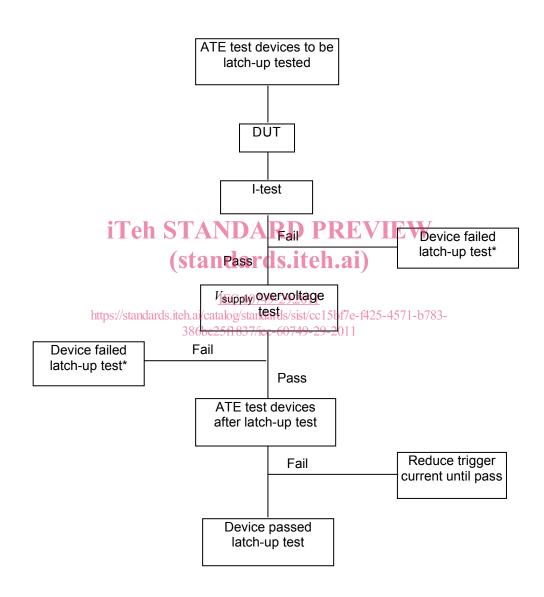

A sample group of devices (e.g. six) shall be subjected to latch-up testing using the l-test and  $V_{supply}$  overvoltage test. The use of a new sample group for each latch-up test type (l-test, and/or  $V_{supply}$  overvoltage test) is also acceptable. All devices to be latch-up tested shall have passed the specified functional and parametric testing.

Before latch-up testing, the device continuity in the socket should be checked to avoid false latch-up failures. The latch-up test flow shall be as shown in Figure 3. The devices to be tested shall be subjected to the test conditions specified in Table 1 and Table 2. All "no connect" pins on the DUT shall be left open (floating) at all times.

All pins on the DUT, with the exception of "no connect" pins and timing related pins, shall be latch-up tested. The input, output and configurable I/O pins shall be tested with the I-test and the  $V_{supply}$  pins tested with the overvoltage test. This includes special pins defined in Annex A. The passing current or voltage values for the special pins can be used for determining the values of the passive-components connected to the pins. I/O pins shall be tested in all possible operating states or the worst case operating state (typically high impedance for configurable I/O pins and output pins).

Dynamic devices shall be tested according to 5.2.3. When a device is sufficiently complex that testing of all configurable I/O pins in the worst case condition is not practicable, the device should be conditioned with a set of vectors representative of the typical operation of the device as determined by engineering judgement. When an I/O pin cannot be tested in the high impedance state, the I/O shall be tested in a valid logic state. Untested pins and pins that could not be completely tested shall be recorded as specified in 5.2.5 and the user shall be informed of all I/O pins that were not tested or tested in all states. After latch-up testing, all devices shall pass the criteria specified in Clause 6.

\* Change in  $I_{\text{supply}}$  exceeds failure criteria in 3.2

IEC 673/11

Figure 3 – Latch-up test flow

| Test<br>type                                    | Trigger<br>polarity         | Condition<br>of<br>untested<br>input pins | Test<br>temperature<br>(±2°C)                 | $V_{supply}$ condition                                                                                                  | Trigger<br>test<br>conditions <sup>9</sup>                                                                | Failure<br>criteria <sup>fg</sup>                                                                                               |

|-------------------------------------------------|-----------------------------|-------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                                                 | Positive<br>see             | Max logic<br>high                         | -                                             | Maximum<br>operating<br>voltage for<br>each V <sub>supply</sub><br>pin group<br>according to<br>device<br>specification | According to classification levels in 3.2 <sup>d</sup>                                                    |                                                                                                                                 |

| I-Test                                          | Figure 6                    | Min logic<br>low                          |                                               |                                                                                                                         |                                                                                                           | If<br>absolute $I_{nom}$<br>is = < 25 mA,<br>then<br>absolute $I_{nom}$<br>+ 10 mA<br>is used<br>or<br>if<br>absolute $I_{nom}$ |

| 1-1651                                          | Negative                    | Max logic<br>high                         | Temperature<br>Class I<br>Room<br>temperature |                                                                                                                         | According to classification levels in 3.2 <sup>e</sup>                                                    |                                                                                                                                 |

|                                                 | Figure 7                    | Min logic<br>low                          |                                               |                                                                                                                         |                                                                                                           |                                                                                                                                 |

| $V_{\sf supply}$                                | See<br>Figure 9             | Logic<br>high                             |                                               |                                                                                                                         | Absolute<br>maximum rating<br>or 1,5<br>maximum V <sub>supply</sub><br>whichever is<br>lower <sup>c</sup> |                                                                                                                                 |

| Over-<br>voltage<br>test                        |                             | Logic<br>Iow                              |                                               |                                                                                                                         |                                                                                                           |                                                                                                                                 |

|                                                 | Positive<br>see             | Max logic<br>high                         |                                               | Maximum                                                                                                                 | According to<br>classification<br>levels in 3.2 <sup>e</sup>                                              |                                                                                                                                 |

| I-Test                                          | Figure 6                    | Min logic<br>Iow                          |                                               |                                                                                                                         |                                                                                                           |                                                                                                                                 |

| I-Test                                          | Negative<br>see<br>Figure 7 | Max logic<br>high                         | Temperature<br>Class II<br>Maximum            | voltage for                                                                                                             | According to<br>classification                                                                            | > 1,4 X<br>absolute I <sub>nom</sub>                                                                                            |

|                                                 |                             | Min logic<br>low                          | operating<br>temperature                      | each V supply<br>pin group<br>according to<br>device                                                                    | levels in 3.2 <sup>e</sup>                                                                                | is used                                                                                                                         |

| V <sub>supply</sub><br>Over-<br>voltage<br>test | See https                   | Max logic<br>://starhighls.iteh           | <u>IEC 60749</u><br>nai/catalog/standa        | -29-20-20-20-20-20-20-20-20-20-20-20-20-20-                                                                             | <sup>1425-4571-6783-</sup><br>1,5 × max<br>V <sub>supply</sub> °                                          |                                                                                                                                 |

|                                                 | Figure 9                    | Min logic <sup>3</sup><br>low             |                                               |                                                                                                                         |                                                                                                           |                                                                                                                                 |

Table 1 – Test matrix<sup>a</sup>

a The trigger conditions herein are not indicative of appropriate trigger conditions for all devices. Appropriate trigger conditions may be more or less stringent. When trigger conditions used in testing differ from this table, the trigger conditions used must be defined in the test results.

- b The  $V_{supply}$  voltage level and ground voltage level shall be applied as the logic high level and logic low level unless otherwise specified in the relevant specification. In the context of a non-digital device, logic levels shall be interpreted as the most appropriate of  $V_{supply}$  voltage, ground voltage or the specified minimum or maximum that may be applied to the pin.

- c Current clamped at ( $I_{nom}$  + 100 mA) or 1,5 ×  $I_{nom}$ , whichever is greater (Refer to 2.11 for max  $V_{supply}$  definition). The  $I_{nom}$  value used for the current clamp calculation relates to the  $V_{supply}$  pin (or pin groups) being tested.

- d Voltage clamped at  $V_{\text{max}}$  + 0,5( $V_{\text{max}}$   $V_{\text{min}}$ ) if  $V_{\text{min}}$  is > 0. Otherwise, the voltage clamp is 1,5  $V_{\text{max}}$ .

- e Voltage clamped at  $V_{\text{max}}$  0,5( $V_{\text{max}} V_{\text{min}}$ ) if  $V_{\text{min}}$  is > 0. Otherwise, the voltage clamp is -0,5  $V_{\text{max}}$ .

- f If the trigger test condition reaches the voltage or current clamp limit and latch-up has not occurred, the pin passes the latch-up test. See Clause 6 for complete failure definition.

- g The  $I_{nom}$  value used for the trigger current calculation relates to the  $V_{supply}$  pin (or pin groups) being tested, not just the  $I_{nom}$  supply for the pin under test.

| Cumhal                                                                                                                         | Time internel       | Demonstern                                           | Limits               |                                               |  |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------|----------------------|-----------------------------------------------|--|--|

| Symbol                                                                                                                         | Time interval       | Parameter                                            | Minimum              | Maximum                                       |  |  |

| t <sub>r</sub>                                                                                                                 |                     | Trigger rise time                                    | 5 μs                 | 5 ms                                          |  |  |

| tf                                                                                                                             |                     | Trigger fall time                                    | 5 µs                 | 5 ms                                          |  |  |

| <i>t</i> width                                                                                                                 | $T3 \rightarrow T4$ | Trigger duration                                     | $2 \times t_{\rm r}$ | 10 ms (I-test)                                |  |  |

|                                                                                                                                |                     | (width)                                              |                      | 5 s (V <sub>supply</sub><br>overvoltage test) |  |  |

| TOS                                                                                                                            |                     | Trigger over-shoot                                   | $\pm 5$ % of pu      | lse voltage                                   |  |  |

| t <sub>cool</sub>                                                                                                              | $T4 \rightarrow T7$ | Cool down time                                       | $\geq t_{width}$     |                                               |  |  |

| t <sub>measure</sub> a                                                                                                         | $T4 \rightarrow T5$ | Waiting time before<br>measuring I <sub>supply</sub> | 3 ms                 | 5s                                            |  |  |

| <sup>a</sup> The wait time should be sufficient to allow for power supply ramp down and stabilization of I <sub>supply</sub> . |                     |                                                      |                      |                                               |  |  |

Table 2 – Timing specifications for I-test and  $V_{supply}$  overvoltage test

#### 5.2 Detailed latch-up test procedure

#### 5.2.1 I-test

The I-test shall be performed as follows:

- a) The devices shall be subjected to the I-test as indicated in Figures 3, 4 and 5 and Tables 1 and 2. (standards.iteh.ai)

- b) Bias the DUT as indicated in Figure 6. All input pins, including bi-directional I/O pins in an input state or high impedance state, not used for preconditioning the I/O pins, shall be tied to the V<sub>supply</sub> voltage level specified, input pins used for preconditioning shall be tested in their defined state (pins that are tied to a logic high level to precondition the DUT can only be tested in the logic-high state; pins that are tied to a logic-low level to precondition the DUT can only be tested in the logic-low state). Allow the DUT to stabilize at the test temperature.

- c) Put the pin under test in logic-high state. Measure nominal  $I_{supply}$  ( $I_{nom}$ ) for each  $V_{supply}$  pin (or pin group, see 2.21). Then, apply the positive current trigger (as specified in Table 1 for a duration as specified in Table 2) to the pin under test.

- d) After the trigger source has been removed, return the pin under test to the state it was in before the application of the trigger pulse, and measure the I<sub>supply</sub> for each V<sub>supply</sub> pin (or pin group). If any I<sub>supply</sub> is greater than or equal to the failure criteria specified in definition 3.2, latch-up has occurred and power shall be removed from the DUT. If latch-up has occurred, stop the test; the DUT has failed latch-up testing. Using a new device, return to step a) and continue testing.

- e) If latch-up has not occurred, after the necessary cool-down time (see Table 2), repeat steps c) and d) for all pins to be tested (noting the exceptions stated in step b)).

- f) Repeat steps b) through e) with all input pins, including bi-directional) I/O pins in an input state or high impedance state, not used for preconditioning the I/O pins tied to ground voltage level.

- g) Bias the DUT as indicated in Figure 7. All input pins, (including bi-directional I/O pins in an input state or high impedance state), that are not used for preconditioning the I/O pins shall be tied to  $V_{supply}$  voltage level specified in the relevant specification (noting the exceptions stated in step b)).

- h) Put the pin under test in logic-low state. Measure nominal  $I_{supply}$  ( $I_{nom}$ ) for each  $V_{supply}$  pin (or pin group, see 2.21). Then, apply the negative current trigger source below ground (in accordance with Table 1 for a duration as specified in Table 2) to the pin under test.

- i) After the trigger source has been removed, return the pin under test to the state it was in before the application of the trigger pulse and measure the  $I_{supply}$  for each  $V_{supply}$  pin (or