Edition 1.0 2017-03

# INTERNATIONAL STANDARD

Semiconductor devices – Mechanical and climatic test methods –

Part 28: Electrostatic discharge (ESD) sensitivity testing – Charged device model (CDM) – device level standards. Iteh. al

<u>IEC 60749-28:2017</u> https://standards.iteh.ai/catalog/standards/sist/0c798383-0d42-4008-933f-22742b9d820e/iec-60749-28-2017

## THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2017 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office Tel.: +41 22 919 02 11 3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch Switzerland www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

## IEC Catalogue - webstore.iec.ch/catalogue

The stand-alone application for consulting the entire bibliographical information on IEC International Standards, Technical Specifications, Technical Reports and other documents. Available for PC, Mac OS, Android Tablets and

## IEC publications search - www.iec.ch/searchpub

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications. standard

### IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and 49 also once a month by emailtps://standards.itch.ai/catalog/standardneed/further assistance/please contact the Customer Service

#### Electropedia - www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing 20 000 terms and definitions in English and French, with equivalent terms in 16 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

#### IEC Glossary - std.iec.ch/glossary

65 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR.

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or 22742b9d820e/iec-Centre: csc@iec.ch.

Edition 1.0 2017-03

## INTERNATIONAL STANDARD

Semiconductor devices – Mechanical and climatic test methods – Part 28: Electrostatic discharge (ESD) sensitivity testing – Charged device model (CDM) – device level

IEC 60749-28:2017 https://standards.iteh.ai/catalog/standards/sist/0c798383-0d42-4008-933f-22742b9d820e/iec-60749-28-2017

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.080.01 ISBN 978-2-8322-4139-4

Warning! Make sure that you obtained this publication from an authorized distributor.

## CONTENTS

| FC | DREWO   | PRD                                                                      | 5  |  |

|----|---------|--------------------------------------------------------------------------|----|--|

| IN | TRODU   | JCTION                                                                   | 7  |  |

| 1  | Scop    | e                                                                        | 8  |  |

| 2  | Norm    | native references                                                        | 8  |  |

| 3  | Term    | is and definitions                                                       | 8  |  |

| 4  |         | Required equipment                                                       |    |  |

| •  | 4.1     | CDM ESD tester                                                           |    |  |

|    | 4.1.1   |                                                                          |    |  |

|    | 4.1.2   |                                                                          |    |  |

|    | 4.1.3   |                                                                          |    |  |

|    | 4.1.4   | ·                                                                        |    |  |

|    | 4.1.5   | •                                                                        |    |  |

|    | 4.2     | Waveform measurement equipment                                           |    |  |

|    | 4.2.1   | · ·                                                                      |    |  |

|    | 4.2.2   |                                                                          |    |  |

|    | 4.2.3   |                                                                          |    |  |

|    | 4.2.4   |                                                                          |    |  |

|    | 4.3     |                                                                          |    |  |

|    | 4.4     | Verification modules (metal discs)                                       | 11 |  |

|    | 4.5     | Ohmmeter (standards.iteh.ai)                                             | 12 |  |

| 5  | Perio   | odic tester qualification, waveform records, and waveform verification   |    |  |

| •  |         | rements <u>IEC 60749-282017</u>                                          | 12 |  |

|    | 5.1     | Overview of required CDM tester evaluations 798383-0d42-4008-933f-       |    |  |

|    | 5.2     | Waveform capture hardware 9d820e/iec-60749-28-2017                       | 12 |  |

|    | 5.3     | Waveform capture setup                                                   |    |  |

|    | 5.4     | Waveform capture procedure                                               | 12 |  |

|    | 5.5     | CDM tester qualification/requalification procedure                       |    |  |

|    | 5.5.1   |                                                                          |    |  |

|    | 5.5.2   |                                                                          |    |  |

|    | 5.5.3   | 1 GHz oscilloscope correlation with high bandwidth oscilloscope          | 14 |  |

|    | 5.6     | CDM tester quarterly and routine waveform verification procedure         | 14 |  |

|    | 5.6.1   | Quarterly waveform verification procedure                                | 14 |  |

|    | 5.6.2   | Routine waveform verification procedure                                  | 14 |  |

|    | 5.7     | Waveform characteristics                                                 | 14 |  |

|    | 5.8     | Documentation                                                            | 16 |  |

|    | 5.9     | Procedure for evaluating full CDM tester charging of a device            | 16 |  |

| 6  | CDM     | ESD testing requirements and procedures                                  | 17 |  |

|    | 6.1     | Device handling                                                          | 17 |  |

|    | 6.2     | Test requirements                                                        |    |  |

|    | 6.2.1   | ·                                                                        |    |  |

|    | 6.2.2   | ·                                                                        |    |  |

|    | 6.3     | Test procedures                                                          |    |  |

|    | 6.4     | CDM test recording / reporting guidelines                                |    |  |

| 7  | CDM     | classification criteria                                                  |    |  |

| Ar | nex A ( | (normative) Verification module (metal disc) specifications and cleaning |    |  |

|    |         | s for verification modules and testers                                   | 19 |  |

| A.1       | Tester verification modules and field plate dielectric                                                    | 19 |

|-----------|-----------------------------------------------------------------------------------------------------------|----|

| A.2       | Care of verification modules                                                                              | 19 |

|           | (normative) Capacitance measurement of verification modules (metal discs) a tester field plate dielectric | 20 |

| Annex C   | (informative) CDM test hardware and metrology improvements                                                | 21 |

| Annex D   | (informative) CDM tester electrical schematic                                                             | 23 |

| Annex E   | (informative) Sample oscilloscope setup and waveform                                                      | 24 |

| E.1       | General                                                                                                   |    |

| E.2       | Settings for the 1 GHz bandwidth oscilloscope                                                             |    |

| E.3       | Settings for the high-bandwidth oscilloscope                                                              |    |

| E.4       | Setup                                                                                                     | 24 |

| E.5       | Sample waveforms from a 1 GHz oscilloscope                                                                | 24 |

| E.6       | Sample waveforms from an 8 GHz oscilloscope                                                               | 25 |

| Annex F   | (informative) Field-induced CDM tester discharge procedures                                               | 27 |

| F.1       | General                                                                                                   | 27 |

| F.2       | Single discharge procedure                                                                                | 27 |

| F.3       | Dual discharge procedure                                                                                  | 27 |

| Annex G   | (informative) Waveform verification procedures                                                            | 29 |

| G.1       | Factor/offset adjustment method                                                                           | 29 |

| G.2       | Software voltage adjustment method.p.p.p.p.p.p.v.v.                                                       | 32 |

| G.3       | Example parameter recording tables                                                                        | 34 |

| Annex H   | (informative) Determining the appropriate charge delay for full charging of a                             |    |

| large mod | dule or device                                                                                            |    |

| H.1       | General <u>IEC.60749-282017</u>                                                                           |    |

| H.2       | Procedure for charge ideray determination t/0c798383-0d42-4008-933f-                                      | 36 |

|           | informative) Electrostatic discharge (ESD) sensitivity testing direct contact device model (DC-CDM)       | 38 |

| l.1       | General                                                                                                   | 38 |

| 1.2       | Standard test module                                                                                      | 38 |

| 1.3       | Test equipment (CDM simulator)                                                                            |    |

| 1.3.1     | Test equipment design                                                                                     | 38 |

| 1.3.2     | , 11                                                                                                      |    |

| 1.3.3     |                                                                                                           |    |

| 1.3.4     | • • •                                                                                                     |    |

| 1.4       | Verification of test equipment                                                                            |    |

| 1.4.1     | General description of verification test equipment                                                        |    |

| 1.4.2     |                                                                                                           |    |

| 1.4.3     |                                                                                                           |    |

| 1.5       | Test procedure                                                                                            |    |

| 1.5.1     | Initial measurement                                                                                       |    |

| 1.5.2     |                                                                                                           |    |

| 1.5.3     |                                                                                                           |    |

| 1.6       | Failure criteria                                                                                          |    |

| 1.7       | Classification criteria                                                                                   |    |

| I.8       | Summary                                                                                                   |    |

| וטווטgra  | ohy                                                                                                       | 44 |

|           |                                                                                                           |    |

| Figure 2 – CDM characteristic waveform and parameters                                                                                       | 16 |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure D.1 – Simplified CDM tester electrical schematic                                                                                     | 23 |

| Figure E.1 – 1 GHz TC 500, small verification module                                                                                        | 25 |

| Figure E.2 – 1 GHz TC 500, large verification module                                                                                        | 25 |

| Figure E.3 – 8 GHz TC 500, small verification module (oscilloscope adjusts for attenuation)                                                 | 26 |

| Figure E.4 – GHz TC 500, large verification module (oscilloscope adjusts for attenuation)                                                   | 26 |

| Figure F.1 – Single discharge procedure (field charging, $I_{\text{CDM}}$ Pulse, and slow discharge)                                        | 27 |

| Figure F.2 – Dual discharge procedure (field charging, 1st $I_{\mbox{CDM}}$ pulse, no field, 2nd $I_{\mbox{CDM}}$ pulse)                    | 28 |

| Figure G.1 – An example of a waveform verification flow for qualification and quarterly checks using the factor/offset adjustment method    | 30 |

| Figure G.2 – An example of a waveform verification flow for the routine checks using the factor/offset adjustment method                    | 31 |

| Figure G.3 – Example of average $I_{\mbox{\scriptsize peak}}$ for the large verification module – high bandwidth oscilloscope               | 32 |

| Figure G.4 – An example of a waveform verification flow for qualification and quarterly checks using the software voltage adjustment method | 33 |

| Figure G.5 – An example of a waveform verification flow for the routine checks using the software voltage adjustment method                 | 34 |

| the software voltage adjustment method                                                                                                      | 37 |

| Figure I.1 – Examples of discharge circuit where the discharge is caused by closing                                                         |    |

| the switch                                                                                                                                  |    |

| Figure I.3 – Current waveform                                                                                                               |    |

| Figure I.4 – Measurement circuit for verification method using a current probe                                                              |    |

| Table 1 – CDM waveform characteristics for a 1 GHz bandwidth oscilloscope                                                                   | 15 |

| Table 2 – CDM waveform characteristics for a high-bandwidth (≥ 6 GHz) oscilloscope                                                          | 15 |

| Table 3 – CDM ESDS device classification levels                                                                                             | 18 |

| Table A.1 – Specification for CDM tester verification modules (metal discs)                                                                 | 19 |

| Table G.1 – Example waveform parameter recording table for the factor/offset adjustment method                                              | 35 |

| Table G.2 – Example waveform parameter recording table for the software voltage adjustment method                                           | 35 |

| Table I.1 – Dimensions of the standard test modules                                                                                         | 38 |

| Table I.2 – Specified current waveform                                                                                                      | 40 |

| Table I.3 – Range of peak current I <sub>p1</sub> for test equipment                                                                        | 41 |

| Table I.4 – Specification of peak current $I_{p1}$ for the current probe verification method                                                | 42 |

## INTERNATIONAL ELECTROTECHNICAL COMMISSION

## SEMICONDUCTOR DEVICES – MECHANICAL AND CLIMATIC TEST METHODS –

## Part 28: Electrostatic discharge (ESD) sensitivity testing – Charged device model (CDM) – device level

## **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

22742b9d820e/iec-60749-28-2017

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-28 has been prepared by IEC technical committee 47: Semiconductor devices in collaboration with IEC technical committee 101: Electrostatics.

This standard is based on ESDA/JEDEC Joint Standard ANSI/ESDA/JEDEC JS-002 which resulted from the merging of JESD22-C101 and ANSI/ESD S5.3.1). It contains the essential elements from both standards. The co-operation of ANSI/ESDA/JEDEC is gratefully acknowledged.

The text of this International Standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 47/2362/FDIS | 47/2379/RVD      |

Full information on the voting for the approval of this International Standard can be found in the report on voting indicated in the above table.

This document has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 60749 series, published under the general title *Semiconductor* devices –Mechanical and climatic test methods, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data related to the specific document. At this date, the document will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

A bilingual version of this publication may be issued at a later date.

(standards.iteh.ai)

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains incolours which at are sconsidered to be useful for the correct understanding of its contents? Users should therefore print this document using a colour printer.

## INTRODUCTION

The earliest electrostatic discharge (ESD) test models and standards simulate a charged object approaching a device and discharging through the device. The most common example is IEC 60749-26, the human body model (HBM). However, with the increasing use of automated device handling systems, another potentially destructive discharge mechanism, the charged device model (CDM), becomes increasingly important. In the CDM, a device itself becomes charged (e.g. by sliding on a surface (tribocharging) or by electric field induction) and is rapidly discharged (by an ESD event) as it closely approaches a conductive object. A critical feature of the CDM is the metal-metal discharge, which results in a very rapid transfer of charge through an air breakdown arc. The CDM test method also simulates metal-metal discharges arising from other similar scenarios, such as the discharging of charged metal objects to devices at different potential.

Accurately quantifying and reproducing this fast metal-metal discharge event is very difficult, if not impossible, due to the limitations of the measuring equipment and its influence on the discharge event. The CDM discharge is generally completed in a few nanoseconds, and peak currents of tens of amperes have been observed. The peak current into the device will vary considerably depending on a large number of factors, including package type and parasitics. The typical failure mechanism observed in MOS devices for the CDM model is dielectric damage, although other damage has been noted.

The CDM charge voltage sensitivity of a given device is package dependent. For example, the same integrated circuit (IC) in a small area package can be less susceptible to CDM damage at a given voltage compared to that same IC in a package of the same type with a larger area. It has been shown that CDM damage susceptibility correlates better to peak current levels than charge voltage.

(standards.iteh.ai)

<u>IEC 60749-28:2017</u> https://standards.iteh.ai/catalog/standards/sist/0c798383-0d42-4008-933f-22742b9d820e/iec-60749-28-2017

## **SEMICONDUCTOR DEVICES -MECHANICAL AND CLIMATIC TEST METHODS -**

## Part 28: Electrostatic discharge (ESD) sensitivity testing -Charged device model (CDM) - device level

#### Scope 1

This part of IEC 60749 establishes the procedure for testing, evaluating, and classifying devices and microcircuits according to their susceptibility (sensitivity) to damage or degradation by exposure to a defined field-induced charged device model (CDM) electrostatic discharge (ESD). All packaged semiconductor devices, thin film circuits, surface acoustic wave (SAW) devices, opto-electronic devices, hybrid integrated circuits (HICs), and multi-chip modules (MCMs) containing any of these devices are to be evaluated according to this document. To perform the tests, the devices are assembled into a package similar to that expected in the final application. This CDM document does not apply to socketed discharge model testers. This document describes the field-induced (FI) method. An alternative, the direct contact (DC) method, is described in Annex I.

The purpose of this document is to establish a test method that will replicate CDM failures and provide reliable, repeatable CDM ESD/test results from tester to tester, regardless of device type. Repeatable data will allow accurate classifications and comparisons of CDM ESD sensitivity levels. (standards.iteh.ai)

## Normative references

IEC 60749-28:2017

https://standards.iteh.ai/catalog/standards/sist/0c798383-0d42-4008-933f-

There are no normative references in this document.

#### Terms and definitions

For the purposes of this document, the following terms and definitions apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at http://www.electropedia.org/

- ISO Online browsing platform: available at http://www.iso.org/obp

## **CDM ESD**

charged device model electrostatic discharge

electrostatic discharge (ESD) using the charged device model (CDM) to simulate the actual discharge event that occurs when a charged device is quickly discharged to another object at a lower electrostatic potential through a single pin or terminal

## 3.2

## **CDM ESD tester**

charged device model electrostatic discharge tester

equipment that simulates the device level CDM ESD event using the non-socketed test method

Note 1 to entry: "Equipment" is referred to as "tester" in this document.

#### 3.3

## dielectric layer

thin insulator placed atop the field plate used to separate the device from the field plate

## 3.4

## field plate

conductive plate used to elevate the potential of the device under test (DUT) by capacitive coupling

Note 1 to entry: See Figure 1.

#### 3.5

## ground plane

conductive plate used to complete the circuitry for grounding/discharging the DUT

Note 1 to entry: See Figure 1.

#### 3.6

## software voltage

user/operator-entered voltage that, when combined with the scale factor or offset, sets the actual field plate voltage on the system in order to achieve the waveform parameters

Note 1 to entry: Waveform parameters are defined in Table 1 or Table 2.

#### 3.7

## test condition

## iTeh STANDARD PREVIEW

TC

tester plate voltage that meets the waveform parameter conditions

Note 1 to entry: The waveform parameter conditions are found in a particular column of Table 1 and Table 2.

https://standards.iteh.ai/catalog/standards/sist/0c798383-0d42-4008-933f-

**4 Required equipment** 22742b9d820e/iec-60749-28-2017

## 4.1 CDM ESD tester

## 4.1.1 General

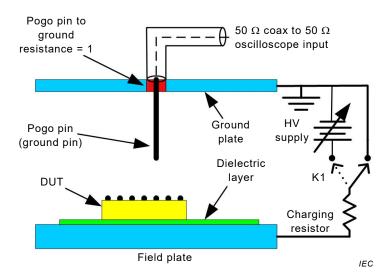

Figure 1 represents the hardware schematic for a CDM tester setup to conduct field-induced CDM ESD testing assuming the use of a resistive current probe. The DUT may be an actual device or it may be one of the two verification modules (metal discs) described in Annex A. The pogo pin shall be connected to the ground plane with a 1  $\Omega$  current path with a minimum bandwidth (BW) of 9 gigahertz (GHz). The 1  $\Omega$  pogo pin to ground connection of the resistive current sensor may be a parallel combination of a 1  $\Omega$  resistor between the pogo pin and the ground plane, and the 50  $\Omega$  impedance of the oscilloscope and its coaxial cable. In Figure 1, K1 is the switch between charging the field plate and grounding the field plate. The CDM ESD testers used within the context of this document shall meet the waveform characteristics specified in Figure 2, and Table 1 and Table 2, without additional passive or active devices, such as ferrites, in the probe's assembly.

Figure 1 - Simplified CDM tester hardware schematic

When constructing the test equipment, the parasitics in the charge and discharge paths should be minimized since the resistance inductance-capacitance (RLC) parasitics in the equipment greatly influence the test results.

For existing equipment, it is recommended to contact qualified service personnel to determine compliance to this document upon removal of ferrite components.

## (standards.iteh.ai)

## 4.1.2 Current-sensing element

A current-sensing element shall be incorporated into the ground plane. The resistance of this element shall have a value of (1,0  $\pm$  10 %)  $\Omega$ . A resistor, as specified in 4.1.1, shall be used as the current-sensing element. The value of resistance (including the 50  $\Omega$  cable/oscilloscope termination) shall be measured using an ohmmeter as described in 4.5. The resistance value shall be used to calculate the first peak current.

The current-sensing element shall have a minimum frequency response of 9 GHz (specified by a maximum roll-off of 3 dB at 9 GHz).

## 4.1.3 Ground plane

The probe assembly shall contain a square ground plane with the probe pin centred within it as shown in Figure 1. The dimensions of the ground plane shall be  $63.5 \text{ mm} \times 63.5 \text{ mm} \pm 6.35 \text{ mm}$  (2.5 inches × 2.5 inches  $\pm$  0.25 inches).

## 4.1.4 Field plate/field plate dielectric layer

The field plate shall have a surface flatness to vary no more than  $\pm$  0,127 mm (0,005 inches). The field plate dielectric layer should be made with an FR4 or similar epoxy-glass material. For FR4, the thickness and thickness tolerance of this dielectric layer should be 0,381 mm  $\pm$  0,0254 mm (0,015 inches  $\pm$  0,001 inches) in order to result in a capacitance measurement (as specified in normative Annex B) in the range specified in Table A.1.

If a different material is used, the material thickness is chosen to result in a capacitance measurement in the range specified in Table A.1.

## 4.1.5 Charging resistor

The charging resistor shown in Figure 1 shall nominally be 100 M $\Omega$  or greater.

Resistor values higher than 100 M $\Omega$  may be used, but this may not allow very large devices (refer to 5.9 and Annex H) to charge fully before being discharged by the probe assembly. This effect can be overcome by adding a delay between discharges in the CDM tester programming software. If using a resistor greater than 100 M $\Omega$ , it is recommended that the tester or the device itself be characterized to determine if a delay is needed for discharging large devices. A procedure for this large device delay characterization is given in Annex H.

## 4.2 Waveform measurement equipment

#### 4.2.1 General

The CDM waveform measurement equipment shall consist of the following components.

#### 4.2.2 Cable assemblies

Cable assemblies with combined internal tester cable and external cable total loss of no more than 2 dB at frequencies up to 9 GHz and a nominal 50  $\Omega$  impedance.

## 4.2.3 Equipment for high-bandwidth waveform measurement

## 4.2.3.1 High-bandwidth oscilloscope ARD PREVIEW

An oscilloscope or transient digitizer with a minimum real-time (single shot) 3 dB BW of at least 6 GHz and  $\geq$  20 gigasample/s sampling rate with a nominal 50  $\Omega$  input impedance.

## 4.2.3.2 Attenuator

IEC 60749-28:2017

https://standards.iteh.ai/catalog/standards/sist/0c798383-0d42-4008-933f-

A 20 dB attenuator with a precision of  $\pm 0.5$  dB)7 at least 712 GHz BW, and an impedance of 50  $\Omega$   $\pm$  5,0  $\Omega$ .

## 4.2.4 Equipment for 1,0 GHz waveform measurement

## 4.2.4.1 1 GHz oscilloscope

An oscilloscope or transient digitizer with a real-time (single shot) 3 dB BW of 1 GHz with a nominal 50  $\Omega$  input impedance. The sampling rate shall be  $\geq$  5 gigasample/s.

NOTE The user has the option of using a higher BW oscilloscope and using a hardware or software filter to produce a bandwidth and sampling rate equivalent to that specified in 4.2.4.1.

## 4.2.4.2 Attenuator

A 20 dB attenuator with a precision of  $\pm$  0,5 dB, at least 4 GHz BW, and an impedance of 50  $\Omega$   $\pm$  5  $\Omega$ .

## 4.3 Verification modules (metal discs)

The large verification module shall have a capacitance of  $(55 \pm 5 \%)$  pF and the small verification module shall have a capacitance of  $(6.8 \pm 5 \%)$  pF. Refer to normative Annex A for information on the verification module physical dimensions and normative Annex B for information on the capacitance measurement procedure.

## 4.4 Capacitance meter

Capacitance meter with a resolution of 0,2 pF, a measurement accuracy of 3 %, and a measurement frequency of 1,0 MHz as described in normative Annex B.