Edition 1.0 2015-08

# PUBLICLY AVAILABLE SPECIFICATION

#### THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2015 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

IEC Central Office Tel.: +41 22 919 02 11 3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch Switzerland www.iec.ch

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

#### About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

#### IEC Catalogue - webstore.iec.ch/catalogue

The stand-alone application for consulting the entire bibliographical information on IEC International Standards, Technical Specifications, Technical Reports and other documents. Available for PC, Mac OS, Android Tablets and

#### IEC publications search - www.iec.ch/searchpub

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications.

#### IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications, Just Published details all new publications released. Available online and also once a month by email.

#### Electropedia - www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 30 000 terms and definitions in English and French, with equivalent terms in 15 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

More than 60 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR.

#### IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need further assistance, please contact the Customer Service Centre: csc@iec.ch.

Edition 1.0 2015-08

## PUBLICLY AVAILABLE SPECIFICATION

INTERNATIONAL ELECTROTECHNICAL COMMISSION

ICS 31.180; 31.190 ISBN 978-2-8322-2808-1

Warning! Make sure that you obtained this publication from an authorized distributor.

### CONTENTS

| FOREWORD |           |                                                                           |        |  |

|----------|-----------|---------------------------------------------------------------------------|--------|--|

| 1        | Scop      | pe                                                                        | 6      |  |

|          | 1.1       | Purpose                                                                   | 7      |  |

|          | 1.2       | Applicable range                                                          | 7      |  |

|          | 1.2.1     | Product                                                                   | 7      |  |

|          | 1.2.2     | Process                                                                   | 8      |  |

|          | 1.3       | Features                                                                  | 9      |  |

|          | 1.3.1     | Maintenance of the device embedded substrate structure                    | 9      |  |

|          | 1.3.2     |                                                                           | 10     |  |

|          | 1.3.3     | embedded device(s)                                                        | 10     |  |

|          | 1.3.4     | including SiP                                                             | 11     |  |

|          | 1.3.5     | Seamless ownership of design data                                         | 11     |  |

| 2        | File      | description                                                               | 12     |  |

|          | 2.1       | File description summary                                                  | 12     |  |

|          | 2.1.1     | Types of data and their structure                                         | 12     |  |

|          | 2.1.2     | 2 File structure                                                          | 14     |  |

|          | 2.2       | 3D expression                                                             | 15     |  |

|          | 2.2.1     | Coordinates                                                               | 15     |  |

|          | 2.2.2     | Position description                                                      | 16     |  |

|          | 2.2.3     | Relation between coordinate origin and board position                     | 16     |  |

|          | 2.3       | Layer concept                                                             | 17     |  |

|          | 2.4       | Substrate data                                                            | 17     |  |

|          | 2.4.1     | Layer map information                                                     | 18     |  |

|          | 2.4.2     | 2 cha Device arrangement information 5.1.4.4.415.8515.41.5.9515.15516.155 | 8.7.19 |  |

|          | 2.4.3     | Basic figures                                                             | 21     |  |

|          | 2.4.4     | Net information                                                           | 28     |  |

|          | 2.4.5     | 5 Artwork information                                                     | 29     |  |

|          | 2.4.6     | Package information                                                       | 29     |  |

|          | 2.4.7     | External port information                                                 | 29     |  |

|          | 2.4.8     | Internal port information                                                 | 29     |  |

|          | 2.4.9     | User expansion information                                                | 29     |  |

|          | 2.5       | Defined data                                                              | 29     |  |

|          | 2.5.1     | Layer definition                                                          | 30     |  |

|          | 2.5.2     | Land definition                                                           | 30     |  |

|          | 2.5.3     | 3 Via definition                                                          | 31     |  |

|          | 2.5.4     | Device definition                                                         | 32     |  |

|          | 2.5.5     | User expansion definition                                                 | 33     |  |

| 3        | Term      | ninology                                                                  |        |  |

| 4        | Com       | mentary – Additional information                                          | 36     |  |

|          |           |                                                                           |        |  |

|          | _         | 1 – Flow chart of design of device embedded substrate                     |        |  |

| Fi       | igure 1.: | 2 – General concept of product                                            | 8      |  |

| Fi       | igure 1.  | 3 – Example of a structure of a device embedded substrate                 | 10     |  |

| Fi       | igure 1.  | 4 – Examples of a structure of a SiP interposer                           | 10     |  |

| Figure 1.5 – Example of a laying terminal position of an embedded device in a virtual layer | 11   |

|---------------------------------------------------------------------------------------------|------|

| Figure 1.6 – Example of showing structures of device embedding and terminals                | 11   |

| Figure 1.7 – Example of showing structures of SiP and of a device                           |      |

| embedding substrate                                                                         |      |

| Figure 2.1 – Data structure                                                                 | 14   |

| Figure 2.2 – One file structure (recommended)                                               | 15   |

| Figure 2.3 – Two-File structure                                                             |      |

| Figure 2.4 – Definition of coordinates                                                      | 16   |

| Figure 2.5 – Position definition                                                            | 16   |

| Figure 2.6 – Relation between coordinates and board position                                | 17   |

| Figure 2.7 – Layer concept                                                                  | . 17 |

| Figure 2.8 – Construction of mounting layers                                                | 18   |

| Figure 2.9 – Construction in the case of omission of mounting layers.                       | 19   |

| Figure 2.10 – Layer definition in pad connection                                            | 20   |

| Figure 2.11 – Layer definition in via connection                                            | 20   |

| Figure 2.12 – XYZ axes rotation direction                                                   | 21   |

| Figure 2.13 – Point                                                                         | . 22 |

| Figure 2.14 – Area shapes                                                                   | 23   |

| Figure 2.15 – Area shapes                                                                   | 23   |

| Figure 2.16 – Letter data                                                                   | 24   |

| Figure 2.17 – Text shape                                                                    | 24   |

| Figure 2.18 – Bonding wire information                                                      | . 25 |

| Figure 2.19 – Wire bonding shape                                                            | 25   |

| Figure 2.20 – Rectangular prismoid                                                          | . 26 |

| Figure 2.21 – Examples of via specification                                                 | 27   |

| Figure 2.22 – Device definition                                                             | 27   |

| Figure 2.23 – Example of group such as dimension lines                                      | 28   |

| Figure 2.24 – Data structure of net information                                             | 28   |

| Figure 2.25 – Relation of layer definition data                                             |      |

| Figure 2.26 – Land definitions                                                              |      |

| Figure 2.27 – Relation between hole information and land information                        |      |

| Figure 2.28 – Definitions of SiP, module and MEMS                                           |      |

| Figure 2.29 – Definitions of package and mold components                                    |      |

| Table 1.1 – Information required in production                                              | . 9  |

| Table 2.1 – List of data                                                                    |      |

|                                                                                             | _    |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### **DEVICE EMBEDDED SUBSTRATE – GUIDELINES – DATA FORMAT**

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

A PAS is a technical specification not fulfilling the requirements for a standard, but made available to the public.

IEC PAS 62878 2-5 was submitted by the JPCA (Japan Electronics Packaging and Circuits Association) and has been processed by IEC technical committee 91: Electronics assembly technology.

It is based on JPCA-EB02 (2011). It is published as a double-logo IEC / JPCA PAS.

The text of this PAS is based on the following document:

This PAS was approved for publication by the P-members of the committee concerned as indicated in the following document

| Draft PAS   | Report on voting |

|-------------|------------------|

| 91/1257/PAS | 91/1264/RVD      |

Following publication of this PAS, which is a pre-standard publication, the technical committee or subcommittee concerned may transform it into an International Standard.

This PAS shall remain valid for an initial maximum period of 3 years starting from the publication date. The validity may be extended for a single period up to a maximum of 3 years, at the end of which it shall be published as another type of normative document, or shall be withdrawn.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

#### DEVICE EMBEDDED SUBSTRATE - GUIDELINES - DATA FORMAT

#### 1 Scope

This part of IEC 62878 defines the data format for active and passive devices embedded inside an organic board whose electrical connections are made by means of a via, electroplating, conductive paste or printing of conductive material. The basic structures, the terminology, reliability tests and a design guide are described in the "Standard of device embedded substrate", JPCA EB01, fourth edition.

A device embedded substrate contains device(s) in the board and is connected in a 3D way. Conventional 2D design technology using GERBER format cannot describe all the connection information in a device embedded substrate. We have several proposals to express 3D data formats but they cannot describe the structures given in EB01. The JPCA Committee for standardization of device embedded substrates has studied various formats and developed a format, FUJIKO V-1.0, which can express substrate design data in CAM data used in actual production. This Publicly Available Specification (PAS) described the FUJIKO data format.

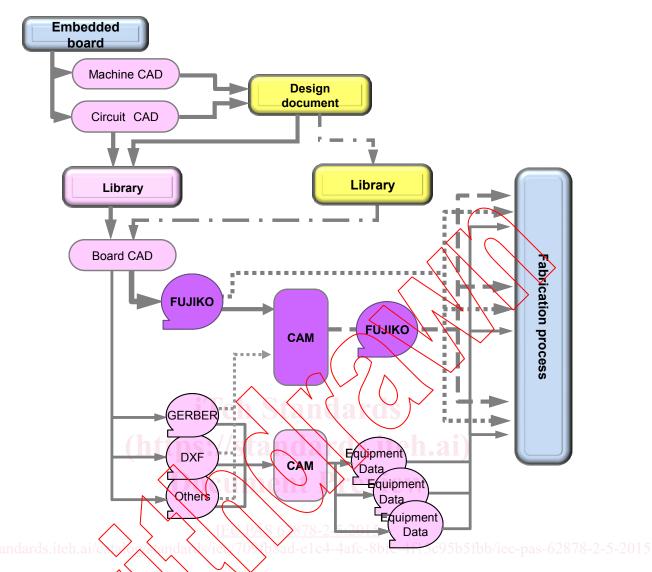

Figure 1.1 shows the design flow of a device embedded substrate. The design data can be directly sent to a board manufacturing system using the FUJIKO format, or can be converted to CAM data and then be used in production. The data contain 3D information of coordinates and shapes of devices used. It is possible to check the status of device embedding in a board, and also make it a common knowledge in production know-how of a production line.

This PAS describes the expression of 3D data information, the concept of layers, the structure of board data, and definitions of information repeatedly used in design.

https://standards.iteh.ai/cva/ov/sindar\s/icv/70\b\8ad-e1c4-4afc-8bfe-4f15c95b5fbb/iec-pas-62878-2-5-2015

Figure 1.1 - Flow chart of design of device embedded substrate

#### 1.1 Purpose

This file format describes the detailed 3D information of the following electronic circuit boards including device embedded substrate and SiP (system in package), and makes it possible to use necessary information from the stage of design to fabrication of products.

#### 1.2 Applicable range

#### 1.2.1 Product

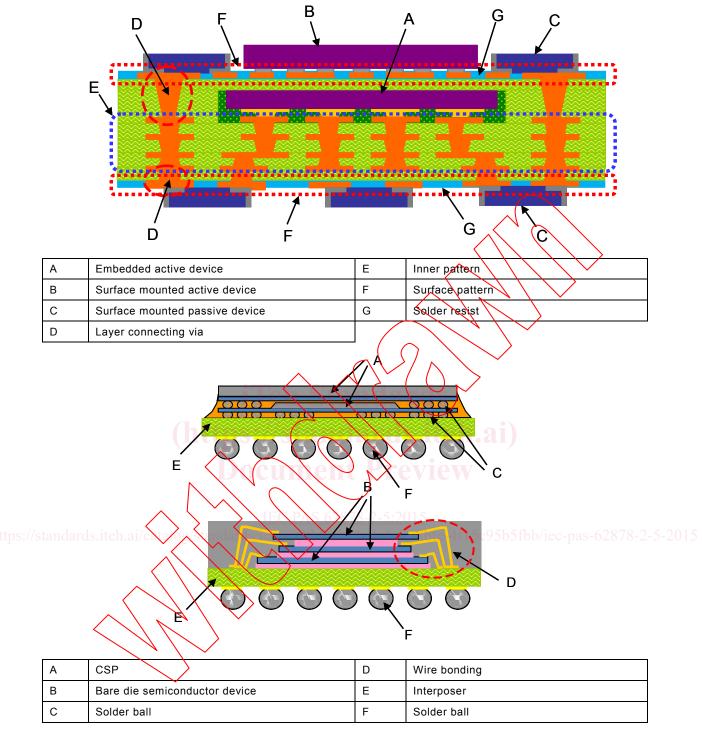

It is possible to maintain the following design information of device embedded substrate as shown in Figure 1.2.

- 1) Information of inside device embedded substrate and surface mounting.

- 2) Assembly information of SiP (System in Package).

Figure 1.2 - General concept of product

#### 1.2.2 Process

The format describes maintained and available information of each stage in production as described in Figure 1.1

- 1) Design

- 2) Simulation

- 3) Substrate fabrication

- 4) Device embedding

- 5) Test.

Table 1.1 - Information required in production

| Process                   | Holding data of                    | Data available for                   |

|---------------------------|------------------------------------|--------------------------------------|

| Design                    | Circuit                            | Limited condition                    |

|                           | Components                         | Net list                             |

|                           | Shape of the board                 |                                      |

|                           | Board structure                    |                                      |

|                           | Design/Production rule (for check) |                                      |

| Simulation                | Circuit                            | Electrical properties                |

|                           | Characteristics of                 | Thermal properties                   |

|                           | components                         | Mechanical properties                |

|                           | Board properties (materials)       | Electronic properties                |

|                           | Board structure                    | Additional information in            |

|                           | Art work                           | production                           |

| Substrate fabrication     | Art work                           | Equipment                            |

|                           | Drilling                           | Additional information in production |

|                           | Symbol marks                       | Arrest /                             |

|                           | Panel format                       |                                      |

| Device embedding          | Component shape                    | Equipment                            |

|                           | Embedding position                 | Relative positions of                |

|                           | Interconnection terminals          | component                            |

| (h                        | Symbol marks                       | Component list                       |

| Test                      | Artwork                            | Electrical test equipment            |

|                           | Component shape                    | Video image inspection               |

|                           | Component position                 |                                      |

|                           | Terminal information 6 878-2-5:201 |                                      |

| andards.iteh.ai/cs/a/og/s | Marks /ie 70 byad-e1c4-4afc-8      | bfe-4f15c95b5fbb/iec-pas-62878-2     |

#### 1.3 Features

Data format has the following characteristics:

- 1) can contain the structure of the device embedding substrate specified in EB01;

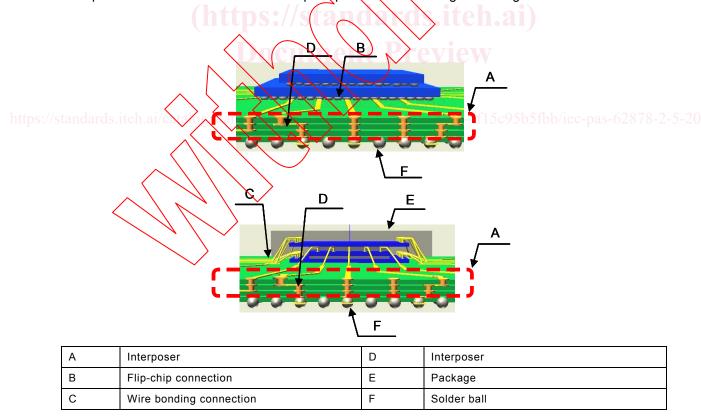

- 2) can contain information of SiP in general (chip stack, PoP TSV, wire bonding, flip-chip, interposer, etc.);

- 3) design data of terminal positions of embedding device in a virtual layer specified in EB01;

- 4) information of internal structure of devices such as SiP which cannot be described as a structure of a device embedded substrate and of a terminal structure as 3D design data;

- 5) seamless keeping of design data of devices having different level such as SiP and of embedding substrate.

#### 1.3.1 Maintenance of the device embedded substrate structure

It is possible to keep and illustrate the 3D structure of device embedded substrate as shown in Figure 1.3. It is also possible to check its 3D structure.

| A | Embedded active device  | D | Pad connection               |

|---|-------------------------|---|------------------------------|

| В | Embedded passive device | E | Space without board material |

| С | Via connection          |   |                              |

Figure 1.3 - Example of a structure of a device embedded substrate

### 1.3.2 Maintenance of SiP interposer structure

It is possible to keep and illustrate the 3D structure of SiP substrate as shown in Figure 1.4. It is also possible to check structures of flip-chip and wire bonding mounting.

Figure 1.4 - Examples of a structure of a SiP interposer

## 1.3.3 Maintenance of design data with a virtual layer of terminal positions of embedded device(s)

It is possible to keep the design data defined in EB01 of the terminal position of a via connection not on a conductor layer, but as in a virtual layer. It can be maintained in the structure shown in Figure 1.5.