Edition 1.0 2018-11

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

Integrated circuits Three dimensional integrated circuits Part 1: Terminology (standards.iteh.ai)

## THIS PUBLICATION IS COPYRIGHT PROTECTED Copyright © 2018 IEC, Geneva, Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch CH-1211 Geneva 20 www.iec.ch

Switzerland

#### About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes International Standards for all electrical, electronic and related technologies.

## **About IEC publications**

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the latest edition, a corrigenda or an amendment might have been published.

## IEC Catalogue - webstore.iec.ch/catalogue

The stand-alone application for consulting the entire bibliographical information on IEC International Standards, Technical Specifications, Technical Reports and other documents. Available for PC, Mac OS, Android Tablets and iPad

## IEC publications search - webstore.iec.ch/advsearchform

The advanced search enables to find IEC publications by a variety of criteria (reference number, text, technical committee,...). It also gives information on projects, replaced and withdrawn publications.

## IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published details all new publications released. Available online and also once a month by email.

## Electropedia - www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing 21/000 terms and definitions in English and French, with equivalent terms in 16 additional languages. Also known as the International Electrotechnical Vocabulary (IEV) online.

## IEC Glossary - std.iec.ch/glossary

67 000 electrotechnical terminology entries in English and French extracted from the Terms and Definitions clause of IEC publications issued since 2002. Some entries have been collected from earlier publications of IEC TC 37, 77, 86 and CISPR.

## IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need further assistance, please contact the Customer Service Centre: sales@jec.ch.

## A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

## A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l'édition la plus récente, un corrigendum ou amendement peut avoir été publié.

## Catalogue IEC - webstore.iec.ch/catalogue

Application autonome pour consulter tous les renseignements bibliographiques sur les Normes internationales, Spécifications techniques, Rapports techniques et autres documents de l'IEC. Disponible pour PC, Mac OS, tablettes Android et iPad.

## Recherche de publications IEC -

## webstore.iec.ch/advsearchform

La recherche avancée permet de trouver des publications IEC en utilisant différents critères (numéro de référence, texte, comité d'études,...). Elle donne aussi des informations sur les projets et les publications remplacées ou retirées.

## IEC Just Published - webstore.iec.ch/justpublished

Restez informé sur les nouvelles publications IEC. Just Published détaille les nouvelles publications parues. Disponible en ligne et aussi une fois par mois par email.

## Electropedia - www.electropedia.org

Le premier dictionnaire en ligne de termes électroniques et électriques. Il contient 21 000 termes et définitions en anglais et en français, ainsi que les termes équivalents dans 16 langues additionnelles. Egalement appelé Vocabulaire Electrotechnique International (IEV) en ligne.

## Glossaire IEC - std.iec.ch/glossary

67 000 entrées terminologiques électrotechniques, en anglais et en français, extraites des articles Termes et Définitions des publications IEC parues depuis 2002. Plus certaines entrées antérieures extraites des publications des CE 37, 77, 86 et CISPR de l'IEC.

## Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions contactez-nous: sales@iec.ch.

Edition 1.0 2018-11

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

Integrated circuits Three dimensional integrated circuits Part 1: Terminology (standards.iteh.ai)

Circuits intégrés – Circuits intégrés tridimensionnels –

Partie 1: Terminologie dards.iteh.ai/catalog/standards/sist/ffloc504b-a891-46b6-a073-b4182b383c75/iec-63011-1-2018

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

ISBN 978-2-8322-6290-0

Warning! Make sure that you obtained this publication from an authorized distributor.

Attention! Veuillez vous assurer que vous avez obtenu cette publication via un distributeur agréé.

## **CONTENTS**

| <b>FOREW</b>            | VORD                          | 3  |

|-------------------------|-------------------------------|----|

|                         | DUCTION                       |    |

|                         | ope                           |    |

| 2 No                    | ormative reference            | 6  |

| 3 Terms and definitions |                               | 6  |

| 3.1                     | General                       | 6  |

| 3.2                     | Test method in 3D environment | 8  |

| Bibliogr                | raphy                         | 12 |

|                         |                               |    |

| Figure 1                | 1 - Evamples of TSVs          | O  |

# iTeh STANDARD PREVIEW (standards.iteh.ai)

IEC 63011-1:2018 https://standards.iteh.ai/catalog/standards/sist/ff0c504b-a891-46b6-a073-b4182b383c75/iec-63011-1-2018

## INTERNATIONAL ELECTROTECHNICAL COMMISSION

## INTEGRATED CIRCUITS – THREE DIMENSIONAL INTEGRATED CIRCUITS –

Part 1: Terminology

## **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user. Standards.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter. https://standards.itch.ai/catalog/standards/sist/ff0c504b-a891-46b6-a073-

- 5) IEC itself does not provide any attestation of conformity independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 63011-1 has been prepared by subcommittee 47A: Integrated circuits, of IEC technical committee 47: Semiconductor devices.

The text of this International Standard is based on the following documents:

| FDIS          | Report on voting |

|---------------|------------------|

| 47A/1060/FDIS | 47A/1064/RVD     |

Full information on the voting for the approval of this International Standard can be found in the report on voting indicated in the above table.

This document has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 63011 series, published under the general title *Integrated Circuits* – *Three dimensional integrated circuits*, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data related to the specific document. At this date, the document will be

- reconfirmed,

- withdrawn,

- · replaced by a revised edition, or

- amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

# iTeh STANDARD PREVIEW (standards.iteh.ai)

IEC 63011-1:2018 https://standards.iteh.ai/catalog/standards/sist/ff0c504b-a891-46b6-a073-b4182b383c75/iec-63011-1-2018

## INTRODUCTION

High performance electrical system requires a massive data exchange between processing integrated circuit (IC) and storage IC. Stacked multiple ICs with a large number of vertical interconnects among dies are an innovative way of providing higher data transfer rate among dies. In addition to bumps, metal pillars, or metal pads which are traditional ways of interconnection between dies, through-silicon vias enable to configure the integration of three or more dies. The integration environment of multichip IC is significantly different from that of the integration on a printed circuit board. This document describes definitions pertaining to the multichip ICs.

# iTeh STANDARD PREVIEW (standards.iteh.ai)

IEC 63011-1:2018 https://standards.iteh.ai/catalog/standards/sist/ff0c504b-a891-46b6-a073-b4182b383c75/iec-63011-1-2018

## INTEGRATED CIRCUITS – THREE DIMENSIONAL INTEGRATED CIRCUITS –

Part 1: Terminology

## 1 Scope

This part of IEC 63011 provides definitions pertaining to multichip integrated circuits, as vertically stacked dies using through-silicon vias (TSVs) or micro bumps. Terms and definitions related to the fabrication and test of the multichip integrated circuits are also provided.

## 2 Normative reference

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

There are no normative references in this document. PREVIEW

(standards.iteh.ai)

## 3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

b4182b383c75/iec-63011-1-2018

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at http://www.electropedia.org/

- ISO Online browsing platform: available at http://www.iso.org/obp

## 3.1 General

The general terms listed below relate to the secondary integration method in vertical direction using integrated circuits fabricated on a horizontal surface of semiconductor.

## 3.1.1

## interposer

electrical interface that connects one socket or connection to another

Note 1 to entry: The purpose of an interposer is to spread a connection to a wider pitch or to reroute a connection to a different connection

## 3.1.2

## multichip interconnect technology

technology that allows for the vertical stacking of layers of basic electronic components which are connected using an interconnect fabric are as follows:

Note 1 to entry: "Basic electronic components" are elementary circuit devices such as transistors, diodes, resistors, capacitors and inductors.

Note 2 to entry: A special case of multichip interconnect technology is the interposer structures that may only contain interconnect layers, although in many cases other basic electronic components (in particular decoupling capacitors) may be embedded into the interposer.

#### 3.1.3

## 3-D bonding

process that joins two die or wafer surfaces together multiple surfaces mechanically or electrically

EXAMPLE: Die-to-die, die-to-wafer, wafer-to-wafer

## 3.1.4

## 3-D stacking

3-D bonding operation that assumes electrical interconnects between the two devices

#### 3.1.5

## 3-D packaging

3-D integration of multiple dies using wire bonding, package-on-package stacking, or embedding in printed circuit boards

#### 3.1.6

## 3-D wafer-level-packaging

## **3-D WLP**

3-D integration using wafer level packaging technologies, performed after wafer fabrication, which consists of flip-chip redistribution, redistribution interconnect, fan-in chip-size packaging, and fan-out reconstructed wafer chip-scale packaging

Note 1 to entry: This note applies to the French language only.

## 3.1.7

## iTeh STANDARD PREVIEW

## redistribution layer

RDI

(standards.iteh.ai)

extra metal layer on a chip that makes the IO pads of an integrated circuit available in other locations  $\underline{\text{IEC } 63011-12018}$

https://standards.iteh.ai/catalog/standards/sist/ff0c504b-a891-46b6-a073-

Note 1 to entry: This note applies to the French anguage only.11-1-2018

## 3.1.8

## system in package

SÍP

integration of multiple dies, packages, or mixture of them as system in a package

Note 1 to entry: This note applies to the French language only.

## 3.1.9

## 3-D stacked integrated circuit

3-D approach using direct interconnects without wire bonding between integrated circuits of multiple dies

Note 1 to entry: The 3-D stack uses a sequence of alternating front-end (devices) and back-end (interconnect) layers.

## 3.1.10

## 3-D integrated circuit

## 3-D IC

3-D approach using direct stacking of active devices

Note 1 to entry: Interconnects are on the local on-chip interconnect levels. The 3-D stack is characterized by a stack of front-end devices, combined with a common back-end interconnect stack.

Note 2 to entry: This note applies to the French language only.

## 3.2 Test method in 3D environment

## 3.2.1

## package stack

integrated circuit packaging method to combine vertically discrete logic and memory ball grid array (BGA) packages

Note 1 to entry: Two or more packages are installed atop each other.

## 3.2.2

## package-on-package

### **POP**

package in which multiple packages are enclosed

Note 1 to entry: This note applies to the French language only.

#### 3.2.3

## multi-chip-package

## **MCP**

package in which multiple dies are stacked vertically or placed side-by-side

Note 1 to entry: This note applies to the French language only.

## 3.2.4

## die stack

chip in which two or more layers of active electronic components are integrated both vertically and horizontally into a single circuit

## (standards.iteh.ai)

## 3.2.5

## contacting die stack

chip in which two or more layers of active electronic components are integrated and signals between multiple layers are transferred via physical and electrical contacts

## 3.2.6

## bump

stud of metal protruded on the surface of die to provide the physical and electrical contact

## 3.2.7

## micro bump

small size bump to make an electrical contact between two dies

## 3.2.8

## flip chip

die mounted with face down

## 3.2.9

## through-silicon via

## TSV

vertical interconnect access passing completely through a silicon wafer or die

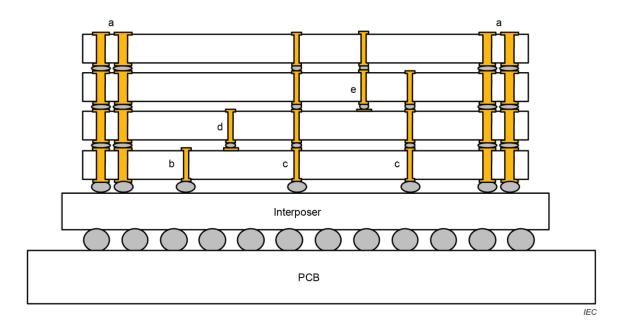

Note 1 to entry: Examples of TSVs are shown in Figure 1.

## Key

- a power TSV;

- b single drop signal TSV;

- c multiple drop signal TSV:Teh STANDARD PREVIEW

- d inter-die jumper;

(standards.iteh.ai)

e stacked inter-die jumper.

## Figure 1: Examples of TSVs

https://standards.iteh.ai/catalog/standards/sist/ff0c504b-a891-46b6-a073-b4182b383c75/iec-63011-1-2018

## 3.2.10

## power TSV

TSV intended to deliver power from one layer to another layer of stacked silicon wafers or dies

Note 1 to entry: Examples are shown in Figure 1.

## 3.2.11

## single drop signal TSV

TSV intended to deliver electric signals from one layer to another layer of stacked silicon wafers or dies

Note 1 to entry: An example is shown in Figure 1.

## 3.2.12

## multiple drop signal TSV

TSV intended to deliver electric signals from one layer to multiple layers of stacked silicon wafers or dies

Note 1 to entry: An example is shown in Figure 1.

## 3.2.13

## inter-die jumper

TSV bridging circuits between adjacent two layers of stacked dies, that is not connected to the output pin of the package

Note 1 to entry: An example is shown in Figure 1.