### SLOVENSKI STANDARD SIST ETS 300 324-1:1997/A1:1997

01-november-1997

Signalizacijski protokoli in komutacija (SPS) - Vmesniki "V" pri digitalnih krajevnih centralah (LE) - Vmesnik V5.1 za podporo dostopovnega omrežja (AN) - 1. del: Specifikacija vmesnika V5.1

Signalling Protocols and Switching (SPS) - V interfaces at the digital Local Exchange (LE); V5.1 interface for the support of Access Network (AN); Part 1: V5.1 interface specification

# iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST ETS 300 324-1:1997/A1:1997 https://standards.iteh.ai/catalog/standards/sist/8706774f-d822-41c1-a2ba-62141495e6f9/sist-ets-300-324-1-1997-a1-1997

Ta slovenski standard je istoveten z: ETS 300 324-1/A1 Edition 1

ICS:

33.040.30 Komutacijski in signalizacijski Switching and signalling

sistem systems

SIST ETS 300 324-1:1997/A1:1997 en

SIST ETS 300 324-1:1997/A1:1997

# iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>SIST ETS 300 324-1:1997/A1:1997</u> https://standards.iteh.ai/catalog/standards/sist/8706774f-d822-41c1-a2ba-62141495e6f9/sist-ets-300-324-1-1997-a1-1997

## **A**MENDMENT

ETS 300 324-1 A1

January 1996

Source: ETSI TC-SPS Reference: RE/SPS-03028

ICS: 33.020, 33.080

Key words: V interface, V5 interface, LE, AN

This amendment A1 modifies the European Telecommunication Standard ETS 300 324-1 (1994)

### iTeh STANDARD PREVIEW

Signalling (Protocols and Switching (SPS);

V interfaces at the digital Local Exchange (LE);

V5.1 interface for the support of Access Network (AN);

Part 1: V5.1 interface specification

#### **ETSI**

European Telecommunications Standards Institute

#### **ETSI Secretariat**

Postal address: F-06921 Sophia Antipolis CEDEX - FRANCE

Office address: 650 Route des Lucioles - Sophia Antipolis - Valbonne - FRANCE

X.400: c=fr, a=atlas, p=etsi, s=secretariat - Internet: secretariat@etsi.fr

Tel.: +33 92 94 42 00 - Fax: +33 93 65 47 16

\*

**Copyright Notification:** No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

SIST ETS 300 324-1:1997/A1:1997

Page 2

ETS 300 324-1: February 1994/A1: January 1996

# iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>SIST ETS 300 324-1:1997/A1:1997</u> https://standards.iteh.ai/catalog/standards/sist/8706774f-d822-41c1-a2ba-62141495e6f9/sist-ets-300-324-1-1997-a1-1997

ETS 300 324-1: February 1994/A1: January 1996

#### **Foreword**

This amendment to ETS 300 324-1 (1994) has been produced by the Signalling Protocols and Switching (SPS) Technical Committee of the European Telecommunications Standards Institute (ETSI).

This amendment contains changes of clauses, subclauses and annexes of ETS 300 324-1 (1994) as detailed below:

Clauses 4 and 5: The general reference to other ETSs and ITU-T Recommendations concerning

the physical/electrical and functional characteristics of the interface layer 1 have to be extended by specifying particular requirements for those aspects having

conceptual implications to the V5.1 interface specification.

Subclause 8.7.3: This subclause uses the term "operational and activated" as state description.

But this state name does not exist.

Amendment: The correct state name is used.

Subclause 10.4.5.5.2: This subclause refers to "different unnumbered commands". Since the only

unnumbered command which may be used for the peer-to-peer procedures of

the data link sublayer, is the SABME command, this term is not applicable.

Subclause 11.1: Editorial error: HDSL has to be replaced by HDLC.

Subclause 13.4.6.3: Table 20 (coding of PSTN FSM state) does not specify the meaning of unused

code points.

Amendment: The usage of all possible code points is clarified.

Subclause 13.4.7.5: Teditorial error: The last sentence of this subclause belongs to figure 24.

Subclause 13.4.7.6: Editorial error. The last sentence of this subclause belongs to figure 25.

Subclause 13.5.2.1: This subclause mentions the code point of the described protocol error cause

value (Protocol discriminator error). The other subclauses which describe the

https://staneling.procedure.dist/87()67741-

Amendment! Delete the mentioning of the code point in subclause 13.5.2.1.

Subclause 13.5.2.10: This subclause has been specified as requiring the generation of two error

indications for one received unexpected event.

If the LE PSTN protocol receives an unexpected event, it shall generate an error

indication and send a STATUS ENQUIRY message.

On receipt of a STATUS message with incompatible path states, the LE shall

generate again an error indication.

Amendment: The requirement for generating two error indications at the LE side

is deleted.

The used term "message sequence error" is ambiguous. Amendment: Delete the term "message sequence error".

Subclause 13.5.3: The used term "message sequence error" is ambiguous.

Amendment: Replace the term "message sequence error" by "unexpected

message".

Subclause 13.5.3.1.1.2: Editorial error: This subclause contains a wrong subclause reference.

Subclause 13.7: The PSTN state tables concerning the handling of unexpected events in state

AN7 are contradictory to subclause 13.5.3.5.1.2 which reflects the basic intention that in state AN7 no reaction on messages other than DISCONNECT and DISCONNECT COMPLETE is to be required, because the PSTN protocol

FSMs are in the clearing down phase and the FSMs will be reset.

But: Table 29 requires that on receipt of PROTOCOL PARAMETER in state

AN7 the sending of a STATUS message is required.

#### Page 4

#### ETS 300 324-1: February 1994/A1: January 1996

Amendment: Table 29, state AN7, event PROTOCOL PARAMETER: No STATUS has to be sent. The text in subclause 13.5.4.1.2 and the SDL diagram in figure L.9.10 are adapted accordingly.

The PSTN state tables create error indications by itself in the case of port blocking or PSTN restart.

If a DISCONNECT COMPLETE message is received in the Port Blocked (AN6/LE6) or Out of Service (AN0/LE0) state of the PSTN protocol, the STATUS/STATUS ENQUIRY procedure will be invoked. As a result, the LE receives a STATUS message. According to table 30, the LE PSTN protocol has then to generate an internal error indication to the LE-system management (table 30: STATUS received in LE0/LE6).

**But:** Upon receipt of MDU-CTRL (port blocked) or MDU-CTRL (restart request), the PSTN protocol has to send a DISCONNECT COMPLETE message before entering the proper state. This applies to both sides. Therefore, it is most likely that one side will receive this message in the Port Blocked or Out of Service state (the port blocking and restart procedure are synchronized by the Control protocol).

Amendment: The handling of STATUS in table 30 is changed.

LE PSTN state table does not cover call collision in the Line Information state. Amendment: Allow the sending of DISCONNECT COMPLETE in state LE2.

Editorial: Note 3 refers to the SDL diagrams. Since the SDL diagrams are only informative, this is an inappropriate reference. As note 3 is not urgently needed to understand the table, it is deleted.

Subclause 14.1.3.4:

Assume a state mismatch of the AN and LE ISDN user port FSMs, such that the AN stays in AN2.2 (access activated) and LE enters LE1.0 (blocked).

If the LE then tries to unblock and synchronize the port by sending FE201, according to table 35 the AN will not send any message over the V5.1 interface and the LE FSM hangs up in state LE1.1 (local unblock).

Amendment: AN sends the response FE104 back to LE.

https://standards.iteh.ai/catalog/standards/sist/8706774f-d822-41c1-a2ba-

Subclause 14.4.1.3:

Note 3 of table 48 is contradictory to table 55. Note 3 of table 48 implies that the variant information element is included in a common control message for the control-function-IDs "blocking started", "restart request" and "restart complete". This is not correct (refer to table 55). Furthermore the information given in the notes of table 48 is redundant.

Amendment: Replace notes 1 to 3 of table 48 by a general note referring to table 55.

Subclause 14.4.4.1:

The fifth paragraph of this subclause uses a wrong state name.

Amendment: The state name is corrected.

Subclause 14.4.4.2.10:

Editorial error: This subclause contains wrong table references.

Annex C, item 2):

Editorial error: This item contains wrong subclause references.

Annex C, item 5):

According to annex C, item 5), the receiving entity of an unblock request message is allowed to send no response back because it does not agree with the unblock request. But then it is not possible for the sender of the unblock request to distinguish between such a disagreement and a mismatch of the port FSMs which has to be resolved by a block-unblock sequence.

Amendment: To avoid a situation where the FSMs stay misaligned and undetected, the receiver of a MPH-UBR shall respond to an unblock request

within a certain time limit.

Annex C, item 12):

The text concerning re-provisioning verification is clarified.

Annex C, item 13):

Initial state of the ISDN user port FSM, PSTN user port FSM and PSTN protocol after system start up is not defined clearly.

Amendment: The system startup procedure is clarified. The SDL diagrams in figures L.9.1, L9.9, L25.1, L25.7 are adapted accordingly.

It is stated that the interface and the variant ID shall be checked during system startup. No procedure exists for the case of an unsuccessful check.

Amendment: The treatment of a unsuccessful system startup is be the same as in the case of an unsuccessful restart (refer to annex C, item 14 b), last paragraph).

Annex C, item 14):

This item defines an asymmetrical PSTN restart procedure (master-slave relationship). This leads to a lock-up situation if the restart is required from both sides at the same point in time.

Amendment: The restart procedure is defined in a symmetrical way. The SDL diagrams in figures L.9.17.4, L17.8, L33.4, L33.8 are adapted accordingly.

Annex C, item 17):

If TC3 expires only on one side of the V5.1 interface, a mismatch of the PSTN protocol FSMs after a re-establishment of the PSTN DL can persist.

Amendment: The PSTN restart procedure is added in case of a reestablishment of the PSTN DL.

Annex C, table C.1:

"Cause for start" of Timer TC2 is wrong. Amendment: The cause for start is corrected.

Annex L, figure L.9.5:

Figure L.9.5 is contradictory to table 29 concerning the handling of an ESTABLISH message in state AN4. Table 29 requires "No action, no state change", figure L.9.5 requires the sending of a STATUS message.

Amendment: Update of figure L.9.5 according to table 29.

Annex L, figure L.17.1:

If during startup the CONTROL\_DL is not able to establish the connection (sending of SABME four times), it sends MDL-RELEASE-INDICATION to system management in figure 17.17, this event is not shown and the required

https://starreaction.of/system.management/is/not/clear-1c1-a2ba-

Amendment of Update of figure 10.17.1 to show the sending of MDL-RELEASE-INDICATION.

Annex L, figure L.17.2:

Figure L.17.2 is contradictory to annex C, item 13), which requires that the variant and interface ID shall be checked during system startup. Figure L.17.2 shows only a check of the interface ID.

Amendment: Update of figure L.17.2 by adding a decision for the correct variant.

The treatment of MDU-CTRL(request variant&interface ID) is missing in states AN1/LE1(SYS).

Amendment: Take into account MDU-CTRL(request variant&interface ID) from AN/LE Control protocol.

The handling of DL release is missing in states AN2/LE2(SYS) (Activate PSTN). Amendment: Take into account MDL-RELEASE-INDICATION from AN/LE PSTN\_DL.

Annex L, figure L.17.7:

The recovery from PSTN\_DL release is not working properly. When MDL-RELEASE-INDICATION is received, timer TC3 is started and MDL-ESTABLISH-REQUEST is sent to PSTN\_DL. When PSTN\_DL receives MDL-ESTABLISH-REQUEST it sends a SABME command over the V5.1 interface. IF PSTN\_DL receives no response, it repeats the SABME three times having breaks of 1 second between each transmission. If PSTN\_DL does not receive any response from the remote side after up to 4 seconds it will send again MDL-RELEASE-INDICATION to system management, which then starts TC3 again and returns MDL-ESTABLISH-REQUEST to PSTN\_DL.

Amendment: TC3 is fixed to 15 seconds, and thus it will never time out.

#### Page 6

#### ETS 300 324-1: February 1994/A1: January 1996

When PSTN\_DL finally manages to re-establish the connection and returns MDL-ESTABLISH-CONFIRMATION to system management, the condition "TC3 running" is insufficient to determine the status of the PSTN ports (blocked or unblocked). Assume that TC3 could time out. The PSTN ports will then be blocked. If MDL-RELEASE-INDICATION is however once more received, TC3 is restarted. Then if MDL-ESTABLISH-CONFIRMATION is received TC3 is running but the port unblock procedure would need to be initiated. Amendment: Update of figure L.17.7 to avoid deadlocks.

Annex L, Figure L25.3: The handling of a call collision in the Line information case is not covered.

Amendment: Show treatment of FE-disconnect\_complete\_request in state LE2.

Annex L, figure L.27.1: Editorial error: The input symbol for PORT CONTROL ACK needs to be flipped.

Annex L, figure L.27.2: Editorial error: Timer TO1 is misspelled.

Annex L, figure L.33.1: Same as figure L.17.1.

Annex L, figure L.33.2: Same as figure L.17.2.

Annex L, figure L.33.5: This figure is not in line with annex C, item 12). MDU-CTRL (blocking started) is

missing

Amendment: Update of figure L.33.5 to include MDU-CTRL (blocking started).

Annex L, figure L.33.7: Same as figure L.17.7.

### Toh CTransposition dates DDFVIFW

Date of adoption of this amendment:

standards.iteh.ai) 12 January 1996

Date of latest announcement of this amendment (doa):

30 April 1996

Date of latest publication or endorsement of this amendment (dop/e): 431 October 1996

Date of withdrawal of any conflicting National Standard (dow):

31 October 1996

ETS 300 324-1: February 1994/A1: January 1996

#### **Amendments**

#### Page 16, clause 2

Add the following normative references:

[8] CCITT Recommendation O.9 (1988): "Measuring arrangements to assess the

degree of unbalance about earth".

[9] CCITT Recommendation O.151 (1992): "Error performance measuring

equipment operating at the primary rate and above".

#### Page 21, clause 4

Replace the complete text of clause 4 by:

"The V5.1 interface consists of a single 2 048 kbit/s interface as defined in ETS 300 166 [1] and ETS 300 167 [2].

The electrical and physical characteristics of the interface shall conform to ETS 300 166 [1], 2 048 kbit/s case.

Two interface presentation alternatives are defined in ETS 300 166 [1], the balanced interface pair type and the coaxial type. According to the two alternatives of interface applications shown in figure 1, it is left to the network operator to request the interface presentation required.

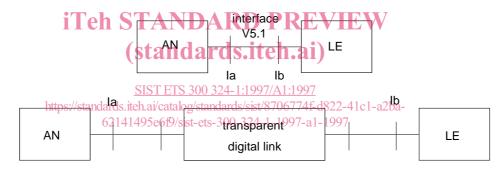

la = interface point at the AN side lb = interface point at the LE side

Figure 1: V5.1 application with and without transparent digital link

This clause identifies the layer 1 requirements from the referenced specifications including the specific characteristics and parameters.

The specific requirements and characteristics from ETS 300 166 [1] and CCITT Recommendation G.703 are listed in table 0a. Where the requirements do not fit into the table, only the reference is shown and the detailed requirements are given below.

#### Page 8

ETS 300 324-1: February 1994/A1: January 1996

Table 0a: Electrical/physical requirements from ETS 300 166 [1] or CCITT Recommendation G.703

| Item      | Requirements based on ETS 300 166 or CCITT Recommendation G.703 | AN                                                          | LE                   |  |  |

|-----------|-----------------------------------------------------------------|-------------------------------------------------------------|----------------------|--|--|

| a)        | Bit rate during operational condition                           | synchronous to LE                                           | synchronous to LE    |  |  |

|           |                                                                 |                                                             | internal clock       |  |  |

| b)        | Bit rate in free running mode                                   | $\leq \pm 50 \text{ ppm}$ $\leq \pm 50 \text{ ppm for AIS}$ |                      |  |  |

| c)        | Code                                                            | HDB3 (annex A/G.703)                                        |                      |  |  |

| d)        | Pulse shape                                                     | figure 15/G.703                                             |                      |  |  |

| e)        | Pairs in each direction                                         | no test                                                     |                      |  |  |

| f)        | Over voltage requirement                                        | annex B/G.703                                               |                      |  |  |

| Ĭ         | - symmetrical interface                                         | figures B-1/G.703 and B-2/G.703                             |                      |  |  |

|           | - coaxial interface                                             |                                                             |                      |  |  |

| g)        | Test load impedance                                             |                                                             |                      |  |  |

|           | - input return loss                                             | 6.3.3/G.703                                                 |                      |  |  |

|           | - output return loss                                            | 5.3 [1]                                                     |                      |  |  |

| h)        | Pulse shape normalized characteristics                          |                                                             |                      |  |  |

|           | <ul> <li>nominal peak voltage of a mark</li> </ul>              |                                                             |                      |  |  |

|           | balanced                                                        | 3 V                                                         |                      |  |  |

|           | coaxial                                                         | 2,37 V                                                      |                      |  |  |

|           | - peak voltage of a space                                       |                                                             |                      |  |  |

|           | balanced                                                        | $0 \pm 0.3 \text{ V}$                                       |                      |  |  |

|           | coaxial                                                         | 0 ± 0,237 V                                                 |                      |  |  |

|           | - nominal pulse width                                           | covered by item d)                                          |                      |  |  |

| i)        | Relative tolerance between consecutive pulses                   |                                                             |                      |  |  |

|           | - ratio of the amplitudes at center of pulse                    | 0,95 to 1,05                                                |                      |  |  |

|           | - ratio of widths at nominal half amplitude                     |                                                             |                      |  |  |

| <u>j)</u> | Maximum output jitter 11 en 51 ANDA                             | high-Q clock, see detaile                                   | d requirements below |  |  |

| k)        | Tolerable longitudinal voltage                                  | de itab ai)                                                 |                      |  |  |

|           |                                                                 | ds <sub>t</sub> iteh.ai)                                    |                      |  |  |

|           | - coaxial interface                                             | not applicable                                              |                      |  |  |

| l)        | Immunity against reflections SIST ETS 300 3                     | 6.3.4/G <sub>7</sub> 703 <sub>1997</sub>                    |                      |  |  |

| m)        | Output signal balancentps://standards.iteh.ai/catalog/stand     | ards/sist/8706774f-d822-41c                                 | 1-a2ba-              |  |  |

|           | - symmetrical interface 62141495e6f9/sist-ets-3                 | <b>9</b> 0 <b>-</b> 324-1-1997-a1-1997                      |                      |  |  |

|           | - coaxial interface                                             | not applicable                                              |                      |  |  |

| n)        | Tolerable input jitter and wander                               | G.823 [7], table 2/G.823                                    |                      |  |  |

| o)        | Connection of outer conductor or screen                         | 6.4/G.703 and table 1/G.                                    | 703, note 7          |  |  |

#### **Detailed requirements for indicated items in table 0a:**

- a) The synchronization of the AN to the LE clock frequency may be through the V5.1 interface or through a synchronization interface. The lock range of the AN shall be  $\geq$  1 ppm and the maximum frequency deviation from the nominal frequency during operation shall be  $\leq$  1 ppm.

- c) The HDB3 code is a modified Alternate Mark Inversion (AMI) code. Binary ONE bits are generally represented by alternate positive and negative pulses, and binary ZERO bits as spaces. Exceptions, as defined for the HDB3 code below, are made when strings of successive ZERO bits occur in the binary signal.

In the definition below, B represents an inserted pulse conforming to the AMI rule and V represents an AMI violation. The encoding of the binary signal in accordance with this rule includes frame alignment bits, etc.

Each block of 4 successive ZEROs shall be replaced by 000V or B00V. The choice of 000V or B00V shall be made so that the number of B pulses between consecutive V pulses is odd, i.e. successive V pulses shall be of alternate polarity so that no dc component is introduced.

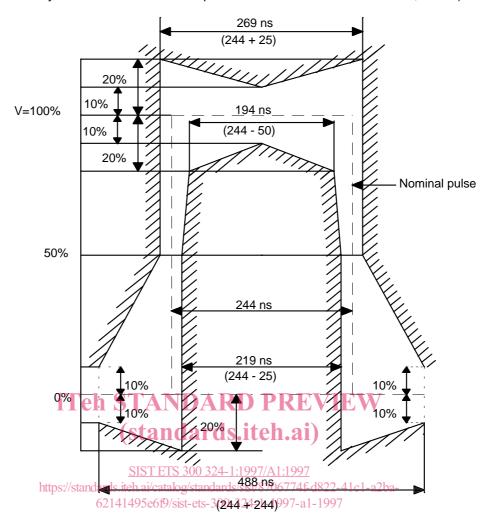

d) The pulse mask given in figure 1a (which is based on figure 15/G.703) shall be met at the output port of the layer 1 interface with the amplitude values as defined in table 0a, item h).

Figure 1a: Mask of the pulse at the output port of the layer 1 interface

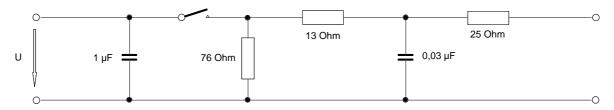

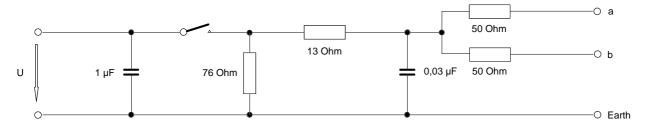

- f) The input and output ports shall withstand without damage the following tests with 10 standard lightning pulses (1,2/50 µs) with a maximum amplitude of U (5 negative and 5 positive impulses).

- 1) at the interface for symmetrical pairs:

- differential mode: with a pulse generator as defined in figure 1b (which is based on figure B-1/G.703), no test value is specified;

- common mode: with a pulse generator as defined in figure 1c (which is based on figure B-2/G.703), U = 100 Vdc.

Figure 1b: Pulse generator 1,2/50 µs for differential mode voltages

#### Page 10 ETS 300 324-1: February 1994/A1: January 1996

Figure 1c: Pulse generator 1,2/50 μs for common mode voltages at symmetrical interfaces

2) at the interface for coaxial pairs:

due to the lack of detailed requirements and test voltages there are no tests defined. However, the pulse generator defined in figure 1b may be used for differential mode voltage test.

g) The input port of the layer 1 interface shall meet the return loss requirements as given in table 0b.

Table 0b: Input port return loss

| Frequency range (kHz) | Return loss (dB) |

|-----------------------|------------------|

| 51 to 102             | ≥ 12             |

| 102 to 2 048          | ≥ 18             |

| 2 048 to 3 072        | ≥ 14             |

The output port of the layer 1 interface shall meet the return loss requirements as given in table 0c.

Table 0c: Output port return loss

| Frequency range (kHz)                   | 00 324 1 1007/A1 10 Return loss (dB)                        |

|-----------------------------------------|-------------------------------------------------------------|

| 51 to 102 //standards itch ai/satalog/s | tandards/sist/8706774f_d822 \(\frac{1}{4}\) \(\frac{1}{4}\) |

| 102 to 3 072 62141495e6f9/sixt          | ets-300-324-1-1997-a1-199 <b>2 8</b>                        |

- j) The output port of the layer 1 interface shall meet the jitter limit of ≤ 0,11 UI when measured with a band-pass with cut-off frequencies at 40 Hz (first order linear high-pass) and 100 kHz with presence of tolerable jitter at the relevant synchronizing input port.

- k) The input port of the layer 1 interface shall meet the requirement for minimum tolerance to longitudinal voltage and the receiver shall operate without errors with any valid input signal in the presence of a longitudinal voltage V<sub>L</sub>.

The test value  $V_L$  shall be 2  $V_{rms}$  over the frequency range 10 Hz to 30 MHz.

I) The input port of the layer 1 interface shall have adequate immunity against reflections that can arise due to impedance irregularities at digital distribution frames and at digital output ports and shall meet the following requirement:

A nominal aggregate signal, encoded into HDB3 and having a pulse shape as defined in the pulse mask, shall have added to it an interfering signal with the same pulse shape as the wanted signal. The interfering signal shall have a bit rate within the limits specified below but shall not be synchronous with the wanted signal. The interfering signal shall be combined with the wanted signal in a combining network, with an overall zero loss in the signal path and with the nominal impedance 75  $\Omega$  (in the case of coaxial-pair interface) or 120  $\Omega$  (in the case of symmetrical-pair interface), to give a signal-to-interference ratio of 18 dB. The binary content of the interfering signal shall comply with CCITT Recommendation 0.151 [9], subclause 2.1 ( $2^{15}$  - 1 bit period). No errors shall result when the combined signal, attenuated by up to the maximum specified interconnecting cable loss, is applied to the input port.

- m) The output port of the layer 1 interface shall meet the output signal balance requirement, which shall be measured in accordance with CCITT Recommendation O.9 [8], subclause 2.7:

- 1) at 1 024 kHz:  $\geq$  40 dB;

- 2) 1 024 kHz to 30 MHz: minimum value decreasing from 40 dB at 20 dB/decade.

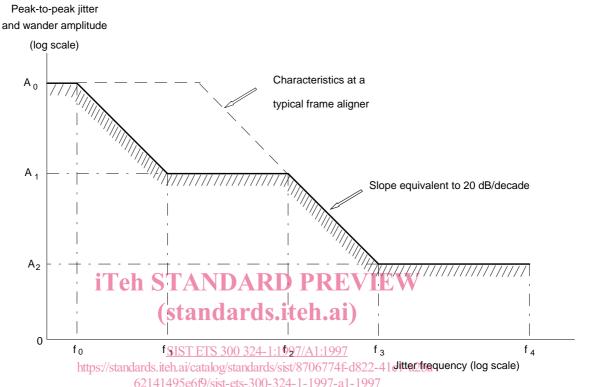

- n) The output port of the layer 1 interface shall meet the jitter and wander requirements defined in figure 1d and table 0d.

Figure 1d: Lower limit of maximum tolerable input jitter and wander

Table 0d: Parameter values for input jitter and wander tolerance

|         | k-to-peak amp<br>(unit interval U |                         | Frequency<br>(Hz)      |                |                       |                      |                       |

|---------|-----------------------------------|-------------------------|------------------------|----------------|-----------------------|----------------------|-----------------------|

| $A_0$   | A <sub>1</sub>                    | A <sub>2</sub>          | f <sub>0</sub>         | f <sub>1</sub> | f <sub>2</sub>        | f <sub>3</sub>       | f <sub>4</sub>        |

| 36,9    | 1,5                               | 0,2                     | 1,2 x 10 <sup>-5</sup> | 20             | 2,4 x 10 <sup>3</sup> | 18 x 10 <sup>3</sup> | 100 x 10 <sup>3</sup> |

| (18 µs) |                                   |                         |                        |                |                       |                      |                       |

| NOTE 1: | 1 UI = 488 ns.                    | =                       |                        |                |                       |                      |                       |

| NOTE 2: | The value for                     | A <sub>0</sub> represen | ts a relative p        | hase deviati   | on between th         | e incoming s         | signal and the        |

NOTE 2: The value for A<sub>0</sub> represents a relative phase deviation between the incoming signal and the internal timing local signal derived from the reference clock.

NOTE 3: The wander requirement of 26 µs takes into account the application of SDH transmission systems providing the transparent digital link between the AN and LE.

The tolerance to jitter of interface inputs shall conform with the requirements for low-Q clock recovery according to CCITT Recommendation G.823 [7]. Interface outputs shall conform with the requirements for high-Q clock recovery according to CCITT Recommendation G.823 [7] even with tolerable input jitter according to low-Q clock recovery, i.e. a jitter reduction capability is required in the frequency area between high-Q and low-Q cut off frequencies for the jitter transfer. This requirement supports independence of the interface implementation from application in networks using different clock recovery Q factors as well as with an additional digital link to increase the range of the interface.

o) The outer conductor of the coaxial pair or the screen of the symmetrical pair shall be connected to the signal ground both at the input and at the output port of the layer 1 interface."