### SLOVENSKI STANDARD SIST EN 60617-12:2000 01-februar-2000

; fUZ| b]'nbU\_]'nU'bU fhY'%&"XY`.'6]bUfb]"c[] b]'Y'Ya Ybh]''f\\97 '\* \$\* %+!%&% - +\2

Graphical symbols for diagrams - Part 12: Binary logic elements (IEC 60617-12:1997)

Graphische Symbole für Schaltpläne - Teil 12: Binäre Elemente (IEC 60617-12:1997)

(standards.iteh.ai)

Ta slovenski standard je istoveten z: EN 60617-12:1998

SIST EN 60617-12:2000

https://standards.iteh.ai/catalog/standards/sisi/b0e30c0d-31b2-40f0-850e-51fdb8c4983c/sist-en-60617-12-2000

ICS:

01.080.40 29.020

SIST EN 60617-12:2000

en,fr

# iTeh STANDARD PREVIEW (standards.iteh.ai)

## EUROPEAN STANDARD NORME EUROPÉENNE EUROPÄISCHE NORM

### EN 60617-12

September 1998

ICS 01.080.30;29.020

Descriptors: Binary logic, logic operation, electric diagram, electrical symbol

English version

Graphical symbols for diagrams

Part 12: Binary logic elements

(IEC 60617-12:1997)

Symboles graphiques pour schémas Partie 12: Eléments logiques binaires (CEI 60617-12:1997) Graphische Symbole für Schaltpläne Teil 12: Binäre Logikbausteine (IEC 60617-12:1997)

This European Standard was approved by CENELEC on 1998-08-01. CENELEC members are bound to comply with the CEN/CENELEC Internal Regulations which stipulate the conditions for giving this European Standard the status of a national standard without any alteration.

Up-to-date lists and bibliographical references concerning such national standards may be obtained on application to the Central Secretariat or to any CENELEC member.

This European Standard exists in three official versions (English, French, German). A version in any other language made by translation under the responsibility of a CENELEC member into its own language and notified to the Central Secretariat has the same status as the official versions.

CENELEC members are the national electrotechnical committees of Austria, Belgium, Czech Republic, Denmark, Finland, France, Germany, Greece, Iceland, Ireland, Italy, Luxembourg, Netherlands, Norway, Portugal, Spain, Sweden, Switzerland and United Kingdom.

<u>SIST EN 60617-12:2000</u> https://standards.iteh.ai/catalog/standards/sist/b0e30c0d-31b2-40f0-850e-51fdb8c4983c/sist-en-60617-12-2000

### **CENELEC**

European Committee for Electrotechnical Standardization Comité Européen de Normalisation Electrotechnique Europäisches Komitee für Elektrotechnische Normung

Central Secretariat: rue de Stassart 35, B - 1050 Brussels

<sup>© 1998</sup> CENELEC - All rights of exploitation in any form and by any means reserved worldwide for CENELEC members.

#### Foreword

The text of document 3A/407/FDIS, future edition 3 of IEC 60617-12, prepared by SC 3A, Graphical symbols for diagrams, of IEC TC 3, Documentation and graphical symbols, was submitted to the IEC-CENELEC parallel vote and was approved by CENELEC on 1996-03-05.

The text of document 3A/431/FDIS, which has been included in the International Standard IEC 60617-12:1997, was submitted to the formal vote (as prAA) and was approved for inclusion in EN 60617-12 on 1998-08-01.

The following dates were fixed:

latest date by which the EN has to be implemented at national level by publication of an identical national standard or by endorsement

(dop) 1999-08-01

latest date by which the national standards conflicting with the EN have to be withdrawn

(dow) 2001-08-01

Annexes designated "normative" are part of the body of the standard. Annexes designated "informative" are given for information only. In this standard, annex ZA is normative and annexes A, B and C are informative. Annex ZA has been added by CENELEC.

#### **Endorsement notice**

The text of the International Standard IEC 60617-12:1997 was approved by CENELEC as a European Standard without any modification.

# iTeh STANDARD PREVIEW (standards.iteh.ai)

#### Annex ZA (normative)

## Normative references to international publications with their corresponding European publications

This European Standard incorporates by dated or undated reference, provisions from other publications. These normative references are cited at the appropriate places in the text and the publications are listed hereafter. For dated references, subsequent amendments to or revisions of any of these publications apply to this European Standard only when incorporated in it by amendment or revision. For undated references the latest edition of the publication referred to applies (including amendments).

NOTE: When an international publication has been modified by common modifications, indicated by (mod), the relevant EN/HD applies.

| Publication  | <u>Year</u> | <u>Title</u>                                                                                                            | EN/HD       | <u>Year</u> |

|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------|-------------|-------------|

| IEC 60617-2  | 1996        | Graphical symbols for diagrams Part 2: Symbol elements, qualifying symbols and other symbols having general application | EN 60617-2  | 1996        |

| IEC 60617-3  | 1996        | Part 3: Conductors and connecting devices                                                                               | EN 60617-3  | 1996        |

| IEC 60617-10 | 1996        | Part 10: Telecommunication: Transmission                                                                                | EN 60617-10 | 1996        |

| IEC 60617-13 | 1993        | Part 13: Analogue elements                                                                                              | EN 60617-13 | 1993        |

| IEC 61082-1  | 1991        | Preparation of documents used in electrotechnology Part 1: General requirements                                         | EN 61082-1  | 1993        |

| IEC 61082-2  | 1993        | Part 2: Function-oriented diagrams                                                                                      | EN 61082-2  | 1994        |

| ISO 31-11    | 1992        | Quantities and units Part 11: Mathematical signs and symbols for use in the physical sciences and technology            | -           | -           |

# iTeh STANDARD PREVIEW (standards.iteh.ai)

# iTeh STANDARD PREVIEW (standards.iteh.ai)

## **NORME** INTERNATIONALE INTERNATIONAL **STANDARD**

CEI **IEC** 60617-12

> Troisième édition Third edition 1997-12

Symboles graphiques pour schémas -

Partie 12:

Opérateurs logiques binaires

Graphical symbols for diagrams -

**Part 12:**

**Binary logic elements**

### iTeh STANDARD PREVIEW

(standards.iteh.ai)

© IEC 1997 Droits de reproduction réservés — Copyright - all rights reserved

Aucune partie de cette publication ne peut être reproduite ni https://stutilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les microfilms, sans l'accord écrit de l'éditeur.

No part of this publication may be reproduced or utilized in any/form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission Telefax: +41 22 919 0300 e-mail: inmail@iec.ch

3, rue de Varembé Geneva, Switzerland IEC web site http://www.iec.ch

Commission Electrotechnique Internationale International Electrotechnical Commission Международная Электротехническая Комиссия

CODE PRIX PRICE CODE

Pour prix, voir catalogue en vigueur For price, see current catalogue

### CONTENTS

|            |                                                                                     | Page<br>7 |  |  |  |

|------------|-------------------------------------------------------------------------------------|-----------|--|--|--|

|            | FOREWORD                                                                            |           |  |  |  |

| INTR       | ODUCTION                                                                            | 9         |  |  |  |

| Chap       | eter I : General                                                                    |           |  |  |  |

| 1          | Scope                                                                               | 11        |  |  |  |

| 1A         | Normative references                                                                | 11        |  |  |  |

| 2          | General notes                                                                       | 11        |  |  |  |

| 3          | Explanation of terms                                                                | 13        |  |  |  |

| Chap       | oter II: Symbol construction                                                        |           |  |  |  |

| 4          | Composition of the symbol                                                           | 15        |  |  |  |

| 5          | Outlines                                                                            | 18        |  |  |  |

| 6          | Use and combination of outlines                                                     | 19        |  |  |  |

| Chap       | oter III: Qualifying symbols associated with inputs, outputs, and other connections |           |  |  |  |

| 7          | Negation, logic polarity and dynamic input                                          | 28        |  |  |  |

| 8          | Internal connections                                                                | 31        |  |  |  |

| 9 .        | Symbols inside the outline                                                          | 38        |  |  |  |

| 10         | Non-logic connections and signal-flow indicators                                    | 69        |  |  |  |

| Chap       | oter IV: Dependency notation                                                        |           |  |  |  |

| 11         | General explanation                                                                 | 72        |  |  |  |

| 12         | Convention                                                                          | 72        |  |  |  |

| 13         | Types of dependency                                                                 | 74        |  |  |  |

| 14         | AND dependency                                                                      | 78        |  |  |  |

| 15         | OR dependency                                                                       | 81        |  |  |  |

| 16         | NEGATE dependency                                                                   | 82        |  |  |  |

| 17         | INTERCONNECTION dependency                                                          | 83        |  |  |  |

| 17A        | TRANSMISSION dependency A ND A R.D. PR.F.V.IEW                                      | 85        |  |  |  |

| 18         | CONTROL dependency SET and RESET dependency tandards.iteh.ai)                       | 88        |  |  |  |

| 19         | SET and RESET dependency tandards. Iten.al)                                         | 90        |  |  |  |

| 20         | ENABLE dependency SIST EN 60617-12:2000 SIST EN 60617-12:2000                       | 93        |  |  |  |

| 21         | MODE dependency standards.iteh.al/catalog/standards/sist/b0e30c0d-31b2-40f0-850e    | 94        |  |  |  |

| 22         | Comparison of C-, EN- and Meffects on inputs 0617-12-2000                           | 98        |  |  |  |

| 23         | ADDRESS dependency                                                                  | 98        |  |  |  |

| 24         | Special techniques used in dependency notation                                      | 104       |  |  |  |

| <b>2</b> 5 | The ordering of labels associated with inputs and with outputs                      | 107       |  |  |  |

| Chap | oter V : Combinative and sequential elements                                                                                                                    |              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 26   | General notes                                                                                                                                                   | 115          |

| 27   | Combinative elements                                                                                                                                            | 116          |

| 28   | Examples of combinative elements                                                                                                                                | 120          |

| 29   | Examples of buffers, drivers, receivers, and bidirectional switches                                                                                             | 126          |

| 30   | Elements with hysteresis                                                                                                                                        | 131          |

| 31   | Examples of elements with hysteresis                                                                                                                            | 131          |

| 32   | Coders, code converters                                                                                                                                         | 133          |

| 33   | Examples of code converters                                                                                                                                     | 144          |

| 34   | Signal-level converters with or without electrical isolation                                                                                                    | 150          |

| 35   | Examples of signal-level converters                                                                                                                             | 150          |

| 36   | Multiplexers and demultiplexers                                                                                                                                 | 151          |

| 37   | Examples of multiplexers and demultiplexers                                                                                                                     | 153          |

| 38   | Arithmetic elements                                                                                                                                             | 157          |

| 39   | Examples of arithmetic elements                                                                                                                                 | 159          |

| 40   | Binary delay elements                                                                                                                                           | 165          |

| 41   | Bistable elements                                                                                                                                               | 167          |

| 42   | Examples of bistable elements                                                                                                                                   | 1 <b>6</b> 9 |

| 43   | Indication of special switching properties of bistable elements                                                                                                 | 173          |

| 44   | Monostable elements                                                                                                                                             | 174          |

| 45   | Examples of monostable elements                                                                                                                                 | 175          |

| 46   | Astable elements                                                                                                                                                | 176          |

| 47   | Examples of astable elements                                                                                                                                    | 178          |

| 48   | Shift registers and counters                                                                                                                                    | 179          |

| 49   | Examples of shift registers and counters                                                                                                                        | 181          |

| 50   | Memories                                                                                                                                                        | 191          |

| 51   | Examples of memories                                                                                                                                            | 193          |

| 52   | Display elements                                                                                                                                                | 203          |

| 53   | Examples of display elements                                                                                                                                    | 205          |

| Cha  | pter VI: Complex-function elements                                                                                                                              |              |

| 54   | General symbol and basic rules and ards. iteh.ai)                                                                                                               | 209          |

| 55   | Bus indicators and data path representation                                                                                                                     | 216          |

| 56   | Examples of complex-function elements 60617-12:2000 https://standards.iteh.ai/catalog/standards/sist/b0e30c0d-31b2-40f0-850e-51fdb8c4983c/sist-en-60617-12-2000 | 220          |

| Ann  | exes .                                                                                                                                                          |              |

| Α    | French alphabetical index                                                                                                                                       | 222          |

| В    | English alphabetical index                                                                                                                                      | 237          |

| С    | Index of devices for which symbols are shown                                                                                                                    | 243          |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### GRAPHICAL SYMBOLS FOR DIAGRAMS -

#### Part 12: Binary logic elements

#### **FOREWORD**

- The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote international cooperation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, the IEC publishes International Standards. Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested National Committees.

- 3) The documents produces have the form of recommendations for international use and are published in the form of standards, technical reports or guides and they are accepted by the National Committees in that sense.

- 4) In order to promote international unification, IEC National Committees undertake to apply. IEC International Standards transparently to the maximum extent possible in their national and regional standards. Any divergence between the IEC Standard and the corresponding national or regional standard shall be clearly indicated in the latter.

- 5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with one of its standards.

- 6) Attention is drawn to the possibility that some of the elements of this International Standard may be the subject of patent rights. The IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60617-12 has been prepared by sub-committee 3A: Graphical symbols for diagrams, of IEC technical committee 3: Documentation and graphical symbols.

This third edition cancels and replaces the second edition, published in 1991, amendment 1 (1992), and amendment 2 (1994). This third edition constitutes a technical revision.

HEN STANDAKD PR

The text of this standard is based on the following documents:

|            | FDIS                                                | Reports on voting                                |         |

|------------|-----------------------------------------------------|--------------------------------------------------|---------|

| https://st | SIST EN 606<br>andards.i <b>3A/407/EDJS</b> :tandar | 17-12:2000<br>rds/sist/ <b>3A/429/RVD</b> b2-40f | )-850e- |

|            | 3A/431/FDIS <sup>/SIST-0</sup>                      | <sup>n-606</sup> 3Ā/463/RVD                      |         |

(standards.iten.ai)

Full information on the voting for the approval of this standard can be found in the reports on voting indicated in the above table.

Annexes A, B and C are for information only.

#### INTRODUCTION

This International Standard forms an element of a series which deals with graphical symbols for diagrams.

The series consists of the following parts:

- Part 1: General information, general index. Cross-reference tables

- Part 2: Symbol elements, qualifying symbols and other symbols having general application

- Part 3: Conductors and connecting devices

- Part 4: Passive components

- Part 5: Semiconductors and electron tubes

- Part 6: Production and conversion of electrical energy

- Part 7: Switchgear, controlgear and protective devices

- Part 8: Measuring instruments, lamps and signalling devices

- Part 9: Telecommunications: Switching and peripheral equipment

- Part 10: Telecommunications: Transmission

- Part 11: Architectural and topographical installation plans and diagrams

- Part 12: Binary logic elements

- Part 13: Analogue elements

# iTeh STANDARD PREVIEW (standards.iteh.ai)

#### **GRAPHICAL SYMBOLS FOR DIAGRAMS -**

Part 12: Binary logic elements

#### Chapter I: General

#### 1 Scope

This part of IEC 60617 contains graphical symbols that have been developed to represent logic functions. They are intended also to represent physical devices or combinations of physical devices capable of carrying out these functions. The symbols have been prepared with a view to electrical applications, but many can also be applied to non-electrical devices, for example pneumatic, hydraulic or mechanical.

#### 1A Normative references

The following normative documents contain provisions which, through reference in this text, constitute provisions of this part of IEC 60617. At the time of publication, the editions indicated were valid. All normative documents are subject to revision, and parties to agreements based on this part of IEC 60617 are encouraged to investigate the possibility of applying the most recent editions of the normative documents listed below. Members of IEC and ISO maintain registers of currently valid International Standards.

IEC 60617-2: 1996, Graphical symbols for diagrams – Part 2: Symbol elements, qualifying symbols and other symbols having general application

IEC 60617-3: 1996, Graphical symbols for diagrams - Part 3: Conductors and connecting devices

IEC 60617-10: 1996, Graphical symbols for diagrams - Part 10: Telecommunication: Transmission

IEC 60617-13: 1993, Graphical symbols for diagrams - Part 13: Analogue elements

IEC 61082-1: 1991, Preparation of documents used in electrotechnology – Part 1: General requirements

IEC 61082-2: 1993, Preparation of documents used in electrotechnology + Part 2: Functionoriented diagrams (Standards.iteh.ai)

ISO 31-11: 1992, Quantities and units – Part 11: Mathematical signs and symbols for use in the physical sciences and technology 2000

https://standards.iteh.ai/catalog/standards/sist/b0e30c0d-31b2-40f0-850e-51fdb8c4983c/sist-en-60617-12-2000

#### 2 General notes

2.1 Symbols in accordance with the superseded IEC 60117-15: Recommended Graphical Symbols, Part 15: Binary Logic Elements, will be required for a prolonged changeover period but should be progressively superseded by the symbols given in this standard. Although non-preferred, the use of other symbols recognized by official national standards, that is distinctive shapes in place of symbols 12-27-01, 12-27-02, 12-27-09, 12-27-10, 12-27-11, 12-27-12, 12-28-01, 12-28-02 and 12-28-04, shall not be considered to be in contradiction with this standard. Usage of these other

symbols in combination to form complex symbols (for example, use as embedded symbols) is discouraged.

- 2.2 For explanation of "logic states", "logic levels", etc., see IEC 61082-2.

- **2.3** This standard uses the symbols 0 and 1 to identify the two logic states of a binary variable. These states are referred to as 0-state and 1-state.

- **2.4** A binary variable may be equated to any physical quantity for which two distinct ranges can be defined. In this standard these distinct ranges are referred to as logic levels and are denoted H and L. H is used to denote the logic level with the more positive algebraic value, and L is used to denote the logic level with the less positive algebraic value.

- 2.5 In the case of a system in which logic states are equated with other qualities of a physical quantity (for example positive or negative pulses, presence or absence of a pulse), H and L may be used to represent these qualities or may be replaced by more suitable designations.

#### 3 Explanation of terms

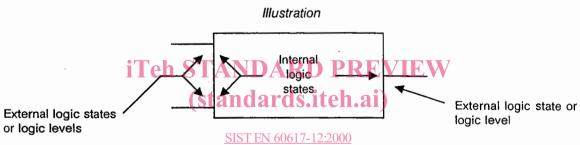

To facilitate understanding of the descriptions in the rest of this standard, it is useful to define three terms.

- 3.1 "Internal logic state" describes a logic state assumed to exist inside a symbol outline at an input or an output.

- 3.2 "External logic state" describes a logic state assumed to exist outside a symbol outline:

- on an input line prior to any external qualifying symbol at that input, or

- on an output line beyond any external qualifying symbol at that output.

- 3.3 "Logic level" describes the physical quality assumed to represent a logic state of a binary variable (see clauses 2.3 and 2.4).

https://standards.iteh.ai/catalog/standards/sist/b0e30c0d-31b2-40f0-850e-51fdb8c4983c/sist-en-60617-12-2000

#### Chapter II: Symbol construction

#### 4 Composition of the symbol

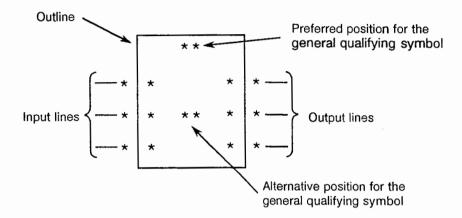

**4.1** A symbol comprises an outline or combination of outlines together with one or more qualifying symbols.

Application of the symbols requires in addition the representation of input and output lines.

The single asterisks (\*) denote possible positions for qualifying symbols relating to inputs and outputs.

If and only if the function of an element is completely determined by the qualifying symbols associated with its inputs and/ or outputs, no general qualifying symbol is needed.

- **4.2** General additional information may be included in a symbol outline as described in IEC 61082-1.

- **4.3** Information not standardized in this standard relating to a specific input [output] may be shown in square brackets inside the outline adjacent to the relevant input [output] and should follow [precede] any qualifying symbols applying to the input [output] as shown in symbol 12-28-14.

Additional information relating to the general logic function of the element may be shown in square brackets inside the outline.

**4.4** All outputs of an element represented by a single unsubdivided symbol always have identical internal logic states determined by the function of the element except when indicated otherwise by an associated qualifying symbol or label inside the symbol outline. The subdivision of a symbol and the qualifying symbols referred to here include those explicitly shown and those only implied according to the simplification rules of clause 6.3.

<u>8181 EN 60617-12:2000</u>

- 4.5 In some figures, lowercase letters which are not part of the symbols have been shown outside the outline just to identify the inputs [outputs] as referred to in the description.

- **4.6** The symbols and descriptions in this standard are intended for signal flow from left to right. If a symbol is instead intended for right-to-left flow, this is explicitly stated in the description of the symbol or indicated in the symbol itself.

When interpreting a symbol, one should assume, unless otherwise indicated, that a terminal shown on the left with respect to the normal reading orientation of the labels inside the symbol is an input,

and that one shown on the right is an output. Inputs may also be shown on the right and outputs on the left if it aids the layout of the diagram or better conveys the structure of the device.

The direction of signal flow shall be clearly implied or indicated. Explicit indication may be done by using qualifying symbols that inherently indicate the direction of signal flow (such as qualifying symbols defined only for inputs or only for outputs, or general qualifying symbols that indicate flow direction) or by other symbols on the diagram that are connected to the terminal.

If the direction of signal flow on a terminal line is not otherwise obvious, that line shall be marked with an arrowhead (symbol 02-05-01 of IEC 60617-2) pointing in the direction of signal flow or with the symbol for bidirectional signal flow (symbol 12-10-02), whichever applies. No arrowhead shall touch the outline or any other qualifying symbol. See, for example, symbol 12-29-06.

**4.7** The following symbols shall be oriented as described or shown within this standard with respect to the inputs, outputs and outlines of the elements in which they appear. That is, these symbols, together with any associated terminal lines, shall be mirrored when the direction of signal flow is reversed:

| 10-15-01  | Amplifier, general symbol (see IEC 60617-10) |

|-----------|----------------------------------------------|

| 12-07-01  | Logic negation, shown at an input            |

| up to and |                                              |

| including |                                              |

| 12-07-09  | Dynamic input with polarity indicator        |

| 12-08-01  | Internal connection                          |

| up to and |                                              |

| including |                                              |

| 12-08-06  | Internal output (virtual output)             |

| 12-09-08A | Output with special amplification            |

| 12-09-08B | Input with special amplification             |

| 12-09-24  | Bit grouping for multibit input              |

| 12-09-25  | Bit grouping for multibit output             |

| 12-09-47  | Line grouping at the input side              |

| 12-09-48  | Line grouping at the output side             |

| 12-55-01  | Bus indicator, unidirectional                |

See, for example, symbol 12-07-03 and its mirrored version 12-07-05.

All other qualifying symbols shall be oriented as shown with respect to the text inside the element.

(standards.iteh.ai)

For more information about the orientation of symbols, see 4.3.4 of IEC 61082-1.

SIST EN 60617-12:2000

https://standards.iteh.ai/catalog/standards/sist/b0e30c0d-31b2-40f0-850e-51fdb8c4983c/sist-en-60617-12-2000