# INTERNATIONAL STANDARD

# ISO/IEC 14443-4

Second edition 2008-07-15 **AMENDMENT 4** 2014-01-15

Identification cards — Contactless integrated circuit cards — Proximity cards —

Part 4: Transmission protocol

# iTeh STAMENDMENTA: Frame with error (storrectionteh.ai)

Cartes d'identification \_\_\_Cartes à circuit(s) intégré(s) sans contact — ISCHEL 1443-4:2008 Amd 4:2014 https://standards.iteh.avcatalog/standards/sist/14d4c476-b877-4d8d-a345-04a1aad2 Partie 4: Protocole de transmission

AMENDEMENT 4: Trame avec correction d'erreur

Reference number ISO/IEC 14443-4:2008/Amd.4:2014(E)

# iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>ISO/IEC 14443-4:2008/Amd 4:2014</u> https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-04a1aad24d76/iso-iec-14443-4-2008-amd-4-2014

#### © ISO/IEC 2014

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Case postale 56 • CH-1211 Geneva 20 Tel. + 41 22 749 01 11 Fax + 41 22 749 09 47 E-mail copyright@iso.org Web www.iso.org

Published in Switzerland

### Foreword

ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards through technical committees established by the respective organization to deal with particular fields of technical activity. ISO and IEC technical committees collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental, in liaison with ISO and IEC, also take part in the work. In the field of information technology, ISO and IEC have established a joint technical committee, ISO/IEC JTC 1.

International Standards are drafted in accordance with the rules given in the ISO/IEC Directives, Part 2.

The main task of the joint technical committee is to prepare International Standards. Draft International Standards adopted by the joint technical committee are circulated to national bodies for voting. Publication as an International Standard requires approval by at least 75 % of the national bodies casting a vote.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights.

Amendment 4 to ISO/IEC 14443-4:2008 was prepared by Joint Technical Committee ISO/IEC JTC 1, *Information technology*, Subcommittee SC 17, *Cards and personal identification*.

## iTeh STANDARD PREVIEW (standards.iteh.ai)

ISO/IEC 14443-4:2008/Amd 4:2014 https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-04a1aad24d76/iso-iec-14443-4-2008-amd-4-2014

# iTeh STANDARD PREVIEW (standards.iteh.ai)

ISO/IEC 14443-4:2008/Amd 4:2014 https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-04a1aad24d76/iso-iec-14443-4-2008-amd-4-2014

# Identification cards — Contactless integrated circuit cards — Proximity cards —

### Part 4: Transmission protocol

### AMENDMENT 4: Frame with error correction

Page 2, NOTE in 3.4

Replace NOTE with

u

NOTE The PICC independent from its type may use the frame with error correction defined in <u>clause 10</u>. Alternatively the PICC Type A may use one of the standard frames defined for Type A and the PICC Type B may use the frame defined for Type B. This Type B frame is called standard frame, too, within this specification.

u

Page 2, Clause 4

### iTeh STANDARD PREVIEW

Add new symbols and abbreviations in alphabetic order h.ai)

| u                 | ISO/IEC 14443-4:2008/Amd 4:2014                                                                                                          |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| A                 | https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-<br>Hamming control.bits generation matrix (6 rows, 56 columns) |

| CRC_32            | Cyclic Redundancy Check error detection code used within enhanced block                                                                  |

| c <sub>n</sub>    | Hamming control bit n                                                                                                                    |

| <u>d</u>          | vector containing 56 data bits                                                                                                           |

| $d_n$             | data bit n                                                                                                                               |

| Н                 | matrix needed to calculate Hamming syndrome <u>s</u> (6 rows, 62 columns)                                                                |

| h' <sub>m,n</sub> | element in row m and column n of matrix <b>H</b> '                                                                                       |

| H'                | matrix needed to get matrix <b>A</b> (6 rows, 62 columns)                                                                                |

| <u>h'n</u>        | column vector of matrix <i>H</i> '                                                                                                       |

| I <sub>6x6</sub>  | 6 by 6 Identity matrix                                                                                                                   |

| LEN               | two bytes LENgth field used within enhanced block                                                                                        |

| n                 | column index                                                                                                                             |

| m                 | row index                                                                                                                                |

| SYNC              | SYNChronization sequence                                                                                                                 |

| <u>S</u>          | 6-bit vector containing Hamming syndrome                                                                                                 |

### ISO/IEC 14443-4:2008/Amd.4:2014(E)

- s' error position code

- s error position

- y 62-bit vector (y' with no padding bits)

- <u>y'</u> 64-bit vector containing received modified Hamming sub-block

- $y'_n$  received bit n in each modified Hamming sub-block

- u

```

Page 14, 7.1

```

Replace first paragraph with

u

The block format depends on the frame format used for its transmission.

The standard block format as specified in Figure 14 shall be used in standard frames as defined in ISO/IEC 14443-3 and consists of:

- a prologue field (mandatory);

- an information field (optional);

- a two-byte epilogue field (mandatory).

The enhanced block format specified in Figure 13 shall be used and rames with error correction as defined in <u>Clause 10</u> and consists of:

ISO/IEC 14443-4:2008/Amd 4:2014

- a length field (mandatory);/standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-

- a prologue field (mandatory); 04a1aad24d76/iso-iec-14443-4-2008-amd-4-2014

- an information field (optional);

- a four-byte epilogue field (mandatory).

- u

### Page 15, after Figure 14

Add a new Figure 15, renumber all figures, add new subclause 7.1.1 and renumber all subsequent subclauses.

u

NOTE The items in brackets indicate optional requirements.

| Length field         | Pr     | ologue fie | ld     | Information field | Epilogue field |  |  |  |  |

|----------------------|--------|------------|--------|-------------------|----------------|--|--|--|--|

| LEN                  | PCB    | [CID]      | [NAD]  | [INF]             | EDC            |  |  |  |  |

| 2 bytes              | 1 byte | 1 byte     | 1 byte |                   | 4 bytes        |  |  |  |  |

| Error Detection Code |        |            |        |                   |                |  |  |  |  |

### Figure 15 — Enhanced block format

### 7.1.1 Length field

The two-byte length field shall contain the total number of bytes contained in the following fields:

- Length field;

- Prologue field;

- Information field. iTeh STANDARD PREVIEW Least significant byte is transmitted first, then most significant byte. (standards.iten.ai) u

```

Page 18, 7.1.3 (renumbered to 7.1.4)SO/IEC 14443-4:2008/Amd 4:2014

https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-

04a1aad24d76/iso-iec-14443-4-2008-amd-4-2014

Replace 7.1.4 with

```

```

"

```

### 7.1.4 Epilogue field

The epilogue field contains the EDC of the transmitted block. A transmitted block shall be considered correct if it is received with a valid EDC value.

The EDC of standard blocks shall be the CRC defined in ISO/IEC 14443-3. Type A PICCs shall use CRC\_A and Type B PICCs shall use CRC\_B in both directions.

The EDC of enhanced blocks shall be CRC\_32 as defined below.

The CRC\_32 uses polynomial = '04C11DB7' with initial value = 'FFFFFFFF' and reflected bit order (LSB first). The final CRC value is bit-inverted before transmission and the least significant byte is transmitted first. Refer to ISO/IEC 13239 for further details. A code sample and an example are given in Annex E.

"

```

Page 23, 7.5.6

```

Replace first sentence with

"When at least one error is detected (after the optional error recovery mechanism see 10.4.7) the following recovery rules shall be applied."

Page 25, before Annex A

Add a new <u>clause 10</u> with the following:

u

### 10 Frame with error correction

### 10.1 General

Frames with error correction as specified in 10.2 and 10.3 shall be used after their activation as specified in 10.5. An example is given in <u>Annex F</u>.

# 10.2 Type A PCD frame format for bit rates up to fc/16 and higher than fc/2 and Type A PICC frame format for all bit rates

Frames with error correction, as defined in Figure 27, shall be used for data exchange and consist of, in the following order:

- start of communication;

- SYNC;

- enhanced block with error correction (see <u>10.4</u>);

- end of communication.

SYNC consists of 6 dedicated bytes with the value '555574747474' transmitted in this order.

SYNC and enhanced blocks with error correction shall be transmitted as bytes consisting of 8 bits.

NOTE Parity bits (see ISO/IEC 14443-3, 6.2.3.2) are not used.teh.ai)

| S                                                                         | SYNC | Enhanced block with error correction         | E |  |  |  |  |

|---------------------------------------------------------------------------|------|----------------------------------------------|---|--|--|--|--|

| https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345- |      |                                              |   |  |  |  |  |

|                                                                           |      | 04a1aad24d76/iso-iec-14443-4-2008-amd-4-2014 |   |  |  |  |  |

Figure 27 — Frame with error correction

# 10.3 Type A PCD frame format for bit rates of fc/8, fc/4 and fc/2 and Type B PCD and PICC frame format for all bit rates

Frames with error correction, as defined in Figure 28, shall be used for data exchange and consist of, in the following order:

- SOF as defined in ISO/IEC 14443-3, 7.1.4;

- SYNC as defined in <u>10.2</u> transmitted as characters as defined in ISO/IEC 14443-3, 7.1.1;

- enhanced block with error correction (see <u>10.4</u>) transmitted as characters as defined in ISO/IEC 14443-3, 7.1.1;

- EOF as defined in ISO/IEC 14443-3, 7.1.5.

No character separation shall be applied in frames with error correction.

SOF, EOF, start bit, stop bit and SYNC may be suppressed in accordance with <u>10.5</u>.

| SOF | SYNC | Enhanced block with error correction | EOF |

|-----|------|--------------------------------------|-----|

|-----|------|--------------------------------------|-----|

Figure 28 — Frame with error correction

### 10.4 Enhanced block with error correction

### 10.4.1 General

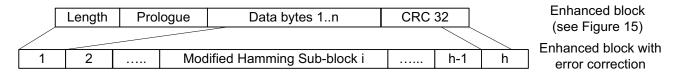

Enhanced block with error correction shall be composed of one or several 8-byte modified Hamming sub-blocks, each of them being calculated from 7-byte sub-blocks from enhanced block (see Figure 29).

#### Figure 29 — Enhanced block with error correction

### 10.4.2 Modified Hamming Sub-block format

Each modified Hamming sub-block shall consist of 7 bytes from enhanced block, followed by one Hamming control byte used to correct one single-bit error on the Hamming sub-block.

Modified Hamming sub-blocks shall always be complete. If necessary, 'FF' bytes shall be added to complete the last bytes from enhanced block to get 7 bytes.

### 10.4.3 Hamming control byte TANDARD PREVIEW

The Hamming control byte shall **contain the Hamming control** bits c<sub>n</sub> and logical "1" padding bits in the following order:

- 1 logical "1" padding bit; <u>ISO/IEC 14443-4:2008/Amd 4:2014</u>

- https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-

- 6 Hamming control bits  $c_n \ln the \overline{order} c_1, c_2, c_3, c_4, c_5, c_6, -4-2014$

- 1 logical "1" padding bit.

An example for Hamming control byte calculation in C language is given in Annex F.2.

### 10.4.4 Hamming control generation matrix A

Hamming control bits generation matrix *A* (see Figure 32) shall be generated by following steps:

- generate Matrix *H*' (see Figure 31) using equation in Figure 30;

- remove column vectors  $\mathbf{h'}_n$ , with n = 1, 2, 4, 8, 16 and 32, of  $\mathbf{H'}$ .

$$\dot{h_{m,n}} = \begin{cases} 1 \text{ for } (n \land 2^{m-1}) \neq 0\\ 0 \text{ otherwise} \end{cases} \text{ with } 1 \le m \le 6 \text{ and } 1 \le n \le 62 \end{cases}$$

### Figure 30 — Matrix H' generation

NOTE ^ stands for a bitwise AND operation.

| <b>H'</b> = | (1 | 0 | 1 | 0 | ••• | 0 | 1 | 0) |

|-------------|----|---|---|---|-----|---|---|----|

|             | 0  | 1 | 1 | 0 |     | 0 | 0 | 1  |

|             | 0  | 0 | 0 | 1 |     | 1 | 1 | 1  |

|             | 0  | 0 | 0 | 0 |     | 1 | 1 | 1  |

|             | 0  | 0 | 0 | 0 |     | 1 | 1 | 1  |

|             | 0  | 0 | 0 | 0 | ••• | 1 | 1 | 1) |

#### Figure 31 — Matrix *H*'

| <b>A</b> = | (1 | 1 | 0 | 1 | ••• | 0 | 1 | 0) |

|------------|----|---|---|---|-----|---|---|----|

|            | 1  | 0 | 1 | 1 |     | 0 | 0 | 1  |

|            | 0  | 1 | 1 | 1 |     | 1 | 1 | 1  |

|            | 0  | 0 | 0 | 0 |     | 1 | 1 | 1  |

|            | 0  | 0 | 0 | 0 |     | 1 | 1 | 1  |

|            | 0  | 0 | 0 | 0 | ••• | 1 | 1 | 1) |

### Figure 32 — Hamming control generation matrix A

### 10.4.5 Hamming control bits calculation

Hamming control bits  $c_m$  (m = 1.6) shall be calculated over data  $d_n$  (n = 1.56) using equation in Figure 33.  $d_1$  is bit b1 of the first byte and  $d_{56}$  is bit b8 of the seventh byte of any 7-byte sub-block from enhanced block.

$\frac{c}{180/1EC} = A \times d$   $\frac{d}{14443-42008/Amd} 4:2014$ https://standards.iteh.ai/catalog/standards/sist/14d4c476-b877-4d8d-a345-Figure 33<sup>120</sup> Hamming control bits generation

### 10.4.6 Hamming control check matrix H

The Hamming control check matrix H (illustrated in Figure 34) is a concatenation of matrix A and matrix  $I_{6x6}$ .

|                      | (1 | 1 | 0 | 1 | ••• | 0 | 1 | 0 | 1 | 0. | 0 | 0) |

|----------------------|----|---|---|---|-----|---|---|---|---|----|---|----|

|                      | 1  | 0 | 1 | 1 |     | 0 | 0 | 1 | 0 | 1  | 0 | 0  |

|                      | 0  | 1 | 1 | 1 |     | 1 | 1 | 1 | 0 | 0  | 0 | 0  |

| $H = H   I_{6,6}$    | 0  | 0 | 0 | 0 |     | 1 | 1 | 1 | 0 | 0  | 0 | 0  |

|                      | 0  | 0 | 0 | 0 |     | 1 | 1 | 1 | 0 | 0  | 1 | 0  |

| $H = A \mid I_{6,6}$ | 0  | 0 | 0 | 0 | ••• | 1 | 1 | 1 | 0 | 0. | 0 | 1) |

### Figure 34 — Hamming control check matrix H

### **10.4.7 Error correction**

Hamming control bits shall be used to detect and correct any single bit error in modified Hamming subblocks.

The so called syndrome <u>s</u> shall be calculated using equation in Figure 35. To get <u>y</u> from <u>y'</u>, the padding bits of the received data  $y'_n$  on position 57 and 64 shall be removed.  $y'_1$  is bit b1 of the first received byte and  $y'_{64}$  is bit b8 of the eighth received byte of any 8-byte sub-block from enhanced block with error correction.

#### $\underline{s} = H \times \underline{y}$

### Figure 35 — Syndrome calculation

The numerical interpretation s' of the syndrome <u>s</u> shall be used for error correction:

- if s' = 0, 1, 2, 4, 8, 16, 32 or 63 no change in received bits  $y'_1$  to  $y'_{56}$

- else

- calculate error position s by reducing s' by the amount of powers of 2 (1, 2, 4, 8, 16, 32) which are smaller than s'

- invert the received bit  $y'_s$

NOTE More than one bit error cannot be corrected by this method. EDC will detect these multiple errors with very high probability.

### 10.5 Activation of frame with error correction in the PROTOCOL state

S(PARAMETERS) blocks shall be used to negotiate the used frame and communication parameters in PROTOCOL state. The following rules shall be applied to negotiate those parameters:

- The information field shall contain tags and values as defined in <u>Tables 4 and 6</u> and <u>Figures 36</u> and <u>37</u>.

- The PCD shall send an S(PARAMETERS) block to request frame format parameters.

- If the PICC supports S(PARAMETERS) blocks, the PICC shall respond with an S(PARAMETERS) block containing values for all supported frame format parameters. If the PICC does not support S(PARAMETERS) it shall stay mute? The PICC shall always indicate the same framing options independent of which tag is used.

After the PICC has sent its response and has indicated its parameters the PCD may activate the desired options for each communication direction with following rules:

- The information field shall contain tags and values as defined in <u>Tables 4 and 6</u> and <u>Figures 36</u> and <u>37</u>.

- The PCD shall send an S(PARAMETERS) block to activate selected frame format parameters.

- The PICC shall acknowledge the activated frame format parameters with an S(PARAMETERS) block and then shall activate the negotiated frame format parameters.

- The PCD shall activate the negotiated frame format parameters.

NOTE 1 S(PARAMETERS) block is defined in ISO/IEC 14443-4:2008/Amd.1:2012.