### SLOVENSKI STANDARD SIST EN 300 462-5-1 V1.1.2:2003

01-december-2003

DfYbcgʻ]bʻa i `hjd`Y\_g]fUb^YʻfHAŁĖ; YbYf] bYʻnU\ hYj YʻnUʻg]b\ fcb]nUV]/g\_Uʻca fYÿ'UË)!%"XY.` Ugcj bYʻnbU ]`bcghjˈdcXfY^Yb]\ 'i fždf]a Yfb]\ 'nUʻcVfUhcj Ub^Yʻj 'cdfYa] g]b\ fcbY`X][]hUʻbY\]YfUf\]^YʻfG8<L

Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 5-1: Timing characteristics of slave clocks suitable for operation in Synchronous Digital Hierarchy (SDH) equipment

## iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST EN 300 462-5-1 V1.1.2:2003 https://standards.iteh.ai/catalog/standards/sist/f4b5e2f2-2779-4880-b2ec-44124e0fc492/sist-en-300-462-5-1-v1-1-2-2003

Ta slovenski standard je istoveten z: EN 300 462-5-1 Version 1.1.2

ICS:

33.040.20 Prenosni sistem Transmission systems

SIST EN 300 462-5-1 V1.1.2:2003 en

SIST EN 300 462-5-1 V1.1.2:2003

# iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST EN 300 462-5-1 V1.1.2:2003 https://standards.iteh.ai/catalog/standards/sist/f4b5e2f2-2779-4880-b2ec-44124e0fc492/sist-en-300-462-5-1-v1-1-2-2003

## EN 300 462-5-1 V1.1.2 (1998-05)

European Standard (Telecommunications series)

Transmission and Multiplexing (TM);

Generic requirements for synchronization networks;

Part 5-1: Timing characteristics of slave clocks suitable for operation in Synchronous Digital Hierarchy (SDH) equipment

## iTeh STANDARD PREVIEW (standards.iteh.ai)

<u>SIST EN 300 462-5-1 V1.1.2:2003</u> https://standards.iteh.ai/catalog/standards/sist/f4b5e2f2-2779-4880-b2ec-44124e0fc492/sist-en-300-462-5-1-v1-1-2-2003

2

### Reference

REN/TM-03017-5-1 (4a199idc.PDF)

### Keywords

synchronization, timing, transmission

#### **ETSI**

#### Postal address

## F-06921/Sophia Antipolis Cedex - FRANCE

## (stan Office address h ai) 650 Route des Lucioles - Sophia Antipolis

Valbonne - FRANCE

Tel.: +3314 92 94 42 00 - Fax: 433 4 93 65 47 16

https://standards.itSiretiNa348\_623.562.000917t/INAF-742 C 779-4880-b2ec-441 Association à but non jucratif enregistrée à la 003 Sous-Préfecture de Grasse (06) N° 7803/88

#### Internet

secretariat@etsi.fr http://www.etsi.fr http://www.etsi.org

### **Copyright Notification**

No part may be reproduced except as authorized by written permission. The copyright and the foregoing restriction extend to reproduction in all media.

> © European Telecommunications Standards Institute 1998. All rights reserved.

## Contents

| Intell                                   | ectual Property Rights                                                                                                                                                                           | 5             |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Forev                                    | word                                                                                                                                                                                             | 5             |

| 1                                        | Scope                                                                                                                                                                                            | 7             |

| 2                                        | References                                                                                                                                                                                       | 7             |

| 3<br>3.1<br>3.2                          | Definitions, symbols and abbreviations  Definitions  Abbreviations                                                                                                                               | 8             |

| 4                                        | Frequency accuracy                                                                                                                                                                               | 8             |

| 5                                        | Pull-in and pull-out ranges                                                                                                                                                                      | 8             |

| 6<br>6.1<br>6.2<br>6.3<br>6.3.1<br>6.3.2 | Noise generation  Wander in locked mode  Non-locked wander  Jitter  Output jitter at a 2 048 kHz and 2 048 kbit/s interface  Output jitter at a Synchronous Transport Module N (STM-N) interface | 9<br>10<br>10 |

| 7<br>7.1<br>7.2                          | Noise tolerance  Jitter tolerance  Wander tolerance :Teh STANDARD PREVIEW                                                                                                                        | 11            |

| 8<br>9<br>9.1<br>9.2                     | Transfer characteristic                                                                                                                                                                          | 14<br>14      |

| 9.3<br>9.4                               | Phase response to input signal interruptions 44124e0fc492/sist-en-300-462-5-1-v1-1-2-2003  Phase discontinuity                                                                                   | 16<br>16      |

| 10                                       | Interfaces                                                                                                                                                                                       | 16            |

| Anne                                     | ex A (informative): Considerations on bandwidth requirements                                                                                                                                     | 18            |

| A.1                                      | Introduction                                                                                                                                                                                     | 18            |

| A.2<br>A.2.1<br>A.2.2<br>A.2.3           | J 1                                                                                                                                                                                              | 18<br>18      |

|                                          |                                                                                                                                                                                                  |               |

| Annex B (informative): Measurement methods for transfer characteristics 21  B.1 Phase step response 22  B.2 Frequency step response 22  B.3 Sinusoidal phase response 22  B.4 White phase noise response (frequency domain) 23  B.5 White phase noise response (time domain) 24  Annex C (informative): Information on the SEC noise model 25  Bibliography 26  History 27 | A.3   | Conclusion                                                           | 20 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------|----|

| B.2 Frequency step response                                                                                                                                                                                                                                                                                                                                                | Anne  | ex B (informative): Measurement methods for transfer characteristics | 21 |

| B.3 Sinusoidal phase response 23 B.4 White phase noise response (frequency domain) 23 B.5 White phase noise response (time domain) 24 Annex C (informative): Information on the SEC noise model 25 Bibliography 26                                                                                                                                                         | B.1   | Phase step response                                                  | 21 |

| B.4 White phase noise response (frequency domain)                                                                                                                                                                                                                                                                                                                          | B.2   | Frequency step response                                              | 22 |

| B.5 White phase noise response (time domain)                                                                                                                                                                                                                                                                                                                               | B.3   | Sinusoidal phase response                                            | 23 |

| Annex C (informative): Information on the SEC noise model                                                                                                                                                                                                                                                                                                                  | B.4   | White phase noise response (frequency domain)                        | 23 |

| Bibliography26                                                                                                                                                                                                                                                                                                                                                             | B.5   | White phase noise response (time domain)                             | 24 |

| ·                                                                                                                                                                                                                                                                                                                                                                          | Anne  | ex C (informative): Information on the SEC noise model               | 25 |

| History                                                                                                                                                                                                                                                                                                                                                                    | Bibli | ography                                                              | 26 |

|                                                                                                                                                                                                                                                                                                                                                                            | Histo | ory                                                                  | 27 |

# iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST EN 300 462-5-1 V1.1.2:2003 https://standards.iteh.ai/catalog/standards/sist/f4b5e2f2-2779-4880-b2ec-44124e0fc492/sist-en-300-462-5-1-v1-1-2-2003

## Intellectual Property Rights

IPRs essential or potentially essential to the present document may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETR 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available **free of charge** from the ETSI Secretariat. Latest updates are available on the ETSI Web server (http://www.etsi.fr/ipr or http://www.etsi.org/ipr).

Pursuant to the ETSI Interim IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETR 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

### **Foreword**

This European Standard (Telecommunications series) has been produced by the Transmission and Multiplexing (TM) Technical Committee.

The present document has been produced to provide requirements for synchronization networks that are compatible with the performance requirements of digital networks. It is one of a family of documents covering various aspects of synchronization networks:

| "Definitions and terminology for synchronization networks";                                                                                                                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "Synchronization network architecture";                                                                                                                                                |

| "The control of jitter and wander within synchronization networks";                                                                                                                    |

| "Timing characteristics of slave clocks suitable for synchronization supply to Synchronous Digital                                                                                     |

| Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) equipment";                                                                                                                 |

| "Timing characteristics of slave clocks suitable for synchronization supply to Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) equipment Implementation |

| Conformance (ICS) Statement";                                                                                                                                                          |

| "Timing characteristics of slave clocks suitable for operation in Synchronous Digital Hierarchy (SDH) equipment";                                                                      |

|                                                                                                                                                                                        |

| "Timing characteristics of primary reference clocks";                                                                                                                                  |

| "Timing characteristics of primary reference clocks";  "Timing characteristics of primary reference clocks Implementation Conformance (ICS) Statement";                                |

|                                                                                                                                                                                        |

Parts 1-1, 2-1, 3-1 and 5-1 have previously been published as ETS 300 462 Parts 1, 2, 3 and 5, respectively.

Additionally, parts 4-1 and 6-1 completed the Voting phase of the Two Step Approval procedure as ETS  $300\,462$  Parts 4 and 6, respectively.

It was decided to prepare ICS proformas for several of the parts and this necessitated a re-numbering of the individual document parts. It was also decided to create a new part 7-1.

This in turn led to a need to re-publish new versions of all six parts of the original ETS. At the same time, the opportunity was taken to convert the document type to EN.

This has involved no technical change to any of the documents. However part 5-1 has been modified, due to editorial errors which appeared in ETS 300 462-5.

EN 300 462-5-1 V1.1.2 (1998-05)

6

| Transposition dates                                                                     |                  |

|-----------------------------------------------------------------------------------------|------------------|

| Date of adoption of this ETS:                                                           | 16 August 1996   |

| Date of latest announcement of this ETS (doa):                                          | 31 December 1996 |

| Date of latest publication of new National Standard or endorsement of this ETS (dop/e): | 30 June 1997     |

| Date of withdrawal of any conflicting National Standard (dow):                          | 30 June 1997     |

NOTE: The above transposition table is the original table from ETS 300 462-5 (September 1996, see History).

# iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST EN 300 462-5-1 V1.1.2:2003 https://standards.iteh.ai/catalog/standards/sist/f4b5e2f2-2779-4880-b2ec-44124e0fc492/sist-en-300-462-5-1-v1-1-2-2003

#### 1 Scope

This European Standard (Telecommunications series) outlines requirements for timing devices used in synchronising network equipment that operates according to the principles governed by the Synchronous Digital Hierarchy (SDH). These requirements apply under the normal environmental conditions specified for SDH equipment. Typical SDH equipment contains a slave clock linked to a master, or a primary reference clock. The logical function of the SEC is described in figure 2 of EN 300 462-2-1 [3]. In general the SDH Equipment Clock (SEC) will have multiple reference inputs. In the event that all links between the master and the slave clock fail, the equipment should be capable of maintaining operation (holdover) within the prescribed performance limits contained within the present document.

Slave clocks used in SDH equipment shall meet specific requirements in order to comply with the jitter specifications given in ETS 300 417-1-1 [9] for plesiochronous tributaries.

The case where clock performance is required in SDH equipment is outside the scope of the present document, see EN 300 462-4-1 [10].

#### References 2

The following documents contain provisions which, through reference in this text, constitute provisions of the present document.

- References are either specific (identified by date of publication, edition number, version number, etc.) or non-specific.

- For a specific reference, subsequent revisions do not apply. PREVIEW

- For a non-specific reference, subsequent revisions do apply (a)

- A non-specific reference to an ETS shall also be taken to refer to later versions published as an EN with the same SIST EN 300 462-5-1 V1.1.2:2003 number.

ETS 300 019: "Equipment Engineering (EE); Environmental conditions and environmental tests

[1] for telecommunications equipment".

https://standards.iteh.ai/catalog/standards/sist/f4b5e2f2-2779-4880-b2ec-

- [2] EN 300 462-1-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 1-1: Definitions and terminology for synchronization networks".

- [3] EN 300 462-2-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 2-1: Synchronisation network architecture".

- [4] ITU-T Recommendation G.823: "The control of jitter and wander within digital networks which are based on the 2 048 kbit/s hierarchy".

- EN 300 462-6-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization [5] networks; Part 6-1: Timing characteristics of primary reference clocks".

- ITU-T Recommendation G.703: "Physical/electrical characteristics of hierarchical digital [6] interfaces".

- [7] ITU-T Recommendation G.825: "The control of jitter and wander within digital networks which are based on the synchronous digital hierarchy (SDH)".

- [8] ITU-T Recommendation Q.551: "Transmission characteristics of digital exchanges".

- [9] ETS 300 417-1-1 (1996): "Transmission and Multiplexing (TM); Generic functional requirements for Synchronous Digital Hierarchy (SDH) equipment; Part 1-1: Generic processes and performance".

- [10] EN 300 462-4-1: "Transmission and Multiplexing (TM); Generic requirements for synchronization networks; Part 4-1: Timing characteristics of slave clocks suitable for synchronization supply to Synchronous Digital Hierarchy (SDH) and Plesiochronous Digital Hierarchy (PDH) equipment".

## 3 Definitions, symbols and abbreviations

### 3.1 Definitions

For the purposes of the present document, the definitions given in EN 300 462-1-1 [2] apply.

### 3.2 Abbreviations

For the purposes of the present document, the abbreviations given in EN 300 462-1-1 [2], together with the following, apply:

MTIE Maximum Time Interval Error NE Network Element

PDH Plesiochronous Digital Hierarchy

PLL Phase Locked Loop

ppm parts per million

PRC Primary Reference Clock

SDH Synchronous Digital Hierarchy

SEC SDH Equipment Clock

SSU Synchronisation Supply Unit

STM-N Synchronous Transport Module N

TDEV Time Deviation UI Unit Interval

UIpp Unit Interval peak to peak NDARD PREVIEW

VCO Voltage Controlled Oscillator

(standards.iteh.ai)

### 4 Frequency accuracy 0 462-5-1 V1.1.2:2003

https://standards.iteh.ai/catalog/standards/sist/f4b5e2f2-2779-4880-b2ec-

Under free-running conditions, the SEC output frequency accuracy shall be within 4,6 ppm with regard to a reference traceable to a clock as specified in EN 300 462-6-1 [5].

NOTE: The time interval for this accuracy specification is for further study.

### 5 Pull-in and pull-out ranges

The minimum pull-in range shall be  $\pm$  4,6 ppm, whatever the internal oscillator frequency offset may be. The Pull-out range is for further study. A value of  $\pm$  4,6 ppm has been proposed.

### 6 Noise generation

The noise generation of a SEC represents the amount of phase noise produced at the output when there is an ideal input reference signal or the clock is in holdover state. A suitable reference, for practical testing purposes, implies a performance level at least 10 times more stable than the output requirements. The ability of the clock to limit this noise is described by its frequency stability. The measures Maximum Time Interval Error (MTIE) and Time Deviation (TDEV) are useful for characterization of noise generation performance.

MTIE and TDEV are measured through an equivalent 10 Hz, first order, low-pass measurement filter, at a maximum sampling time  $t_0$  of 1/30 second. The minimum measurement period for TDEV is twelve times the integration period (T = 12 $\tau$ ).

### 6.1 Wander in locked mode

When the SEC is in the locked mode of operation, the MTIE and TDEV measured using the synchronised clock configuration defined in figure 1a of EN 300 462-1-1 [2] shall have the limits in tables 1 and 2, if the temperature is constant ( $\pm$  1 K).

Table 1: Wander in locked mode for constant temperature specified in MTIE

| Requirement                 | Observation interval         |

|-----------------------------|------------------------------|

| 40 ns                       | $0.1 < \tau \le 1 \text{ s}$ |

| $40  \tau^{0,1}  \text{ns}$ | $1 < \tau \le 100 \text{ s}$ |

| $25 \tau^{0,2} \text{ ns}$  | $100 < \tau \le 1\ 000\ s$   |

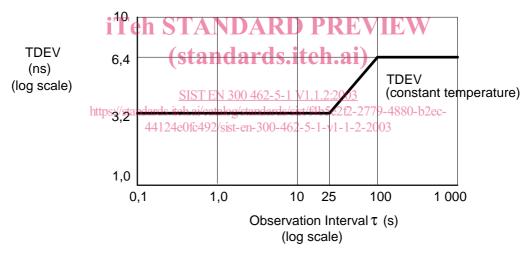

Table 2: Wander in locked mode for constant temperature specified in TDEV

| Requirement                       | Observation interval          |

|-----------------------------------|-------------------------------|

| 3,2 ns                            | $0.1 < \tau \le 25 \text{ s}$ |

| $0,64 \text{ t}^{0,5} \text{ ns}$ | $25 < \tau \le 100 \text{ s}$ |

| 6,4 ns                            | $100 < \tau \le 1\ 000\ s$    |

The model used to derive these numbers is described in (informative) annex C. The resultant requirements are shown by the thick solid lines in figures 1 and 2.

Figure 1: TDEV as a function of an observation period  $\tau$