### SLOVENSKI STANDARD SIST EN IEC 62228-6:2023

01-februar-2023

Integrirana vezja - Vrednotenje elektromagnetne združljivosti (EMC) oddajnikovsprejemnikov - 6. del: Oddajniki-sprejemniki PSI5 (IEC 62228-6:2022)

Integrated circuit - EMC Evaluation of transceivers - Part 6: PSI5 transceivers (IEC 62228-6:2022)

Integrierte Schaltungen - EMV-Bewertung von Transceivern - Teil 6: PSI5-Transceiver (IEC 62228-6:2022)

Circuits intégrés - Évaluation de la CEM des émetteurs-récepteurs - Partie 6: Émetteurs-récepteurs PSI5 (IEC 62228-6:2022)

Ta slovenski standard je istoveten z: EN IEC 62228-6:2022

ICS:

31.200 Integrirana vezja, Integrated circuits. mikroelektronika Microelectronics

33.100.01 Elektromagnetna združljivost Electromagnetic compatibility

na splošno in general

SIST EN IEC 62228-6:2023 en

**SIST EN IEC 62228-6:2023**

# iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST EN IEC 62228-6:2023

https://standards.iteh.ai/catalog/standards/sist/8b280d30-6ac7-4854-842d-40fce3dbcdc2/sist-en-iec-62228-6-2023

EUROPEAN STANDARD NORME EUROPÉENNE FUROPÄISCHE NORM **EN IEC 62228-6**

December 2022

ICS 31.200

#### **English Version**

# Integrated circuit - EMC evaluation of transceivers - Part 6: PSI5 transceivers (IEC 62228-6:2022)

Circuits intégrés - Évaluation de la CEM des émetteursrécepteurs - Partie 6: Émetteurs-récepteurs PSI5 (IEC 62228-6:2022) Integrierte Schaltungen - EMV-Bewertung von Transceivern - Teil 6: PSI5-Transceiver (IEC 62228-6:2022)

This European Standard was approved by CENELEC on 2022-12-13. CENELEC members are bound to comply with the CEN/CENELEC Internal Regulations which stipulate the conditions for giving this European Standard the status of a national standard without any alteration.

Up-to-date lists and bibliographical references concerning such national standards may be obtained on application to the CEN-CENELEC Management Centre or to any CENELEC member.

This European Standard exists in three official versions (English, French, German). A version in any other language made by translation under the responsibility of a CENELEC member into its own language and notified to the CEN-CENELEC Management Centre has the same status as the official versions.

CENELEC members are the national electrotechnical committees of Austria, Belgium, Bulgaria, Croatia, Cyprus, the Czech Republic, Denmark, Estonia, Finland, France, Germany, Greece, Hungary, Iceland, Ireland, Italy, Latvia, Lithuania, Luxembourg, Malta, the Netherlands, Norway, Poland, Portugal, Republic of North Macedonia, Romania, Serbia, Slovakia, Slovenia, Spain, Sweden, Switzerland, Türkiye and the United Kingdom.

European Committee for Electrotechnical Standardization Comité Européen de Normalisation Electrotechnique Europäisches Komitee für Elektrotechnische Normung

CEN-CENELEC Management Centre: Rue de la Science 23, B-1040 Brussels

#### EN IEC 62228-6:2022 (E)

### **European foreword**

The text of document 47A/1145/FDIS, future edition 1 of IEC 62228-6, prepared by SC 47A "Integrated circuits" of IEC/TC 47 "Semiconductor devices" was submitted to the IEC-CENELEC parallel vote and approved by CENELEC as EN IEC 62228-6:2022.

The following dates are fixed:

- latest date by which the document has to be implemented at national (dop) 2023-09-13 level by publication of an identical national standard or by endorsement

- latest date by which the national standards conflicting with the document have to be withdrawn (dow) 2025-12-13

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. CENELEC shall not be held responsible for identifying any or all such patent rights.

Any feedback and questions on this document should be directed to the users' national committee. A complete listing of these bodies can be found on the CENELEC website.

#### **Endorsement notice**

### iTeh STANDARD PREVIEW

The text of the International Standard IEC 62228-6:2022 was approved by CENELEC as a European Standard without any modification.

SIST EN IEC 62228-6:2023

https://standards.iteh.ai/catalog/standards/sist/8b280d30-6ac7-4854-842d 40fce3dbcdc2/sist-en-iec-62228-6-2023

EN IEC 62228-6:2022 (E)

## Annex ZA (normative)

# Normative references to international publications with their corresponding European publications

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

NOTE 1 Where an International Publication has been modified by common modifications, indicated by (mod), the relevant EN/HD applies.

NOTE 2 Up-to-date information on the latest versions of the European Standards listed in this annex is available here: www.cenelec.eu.

| <u>Publication</u> | <u>Year</u>   | <u>Title</u>                                                                                                                                       | EN/HD          | <u>Year</u> |

|--------------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------|

| IEC 61967-1        | -             | Integrated circuits - Measurement of electromagnetic emissions - Part 1: General conditions and definitions                                        | EN IEC 61967-1 | -           |

| IEC 61967-4        | iTe           | Integrated circuits - Measurement of electromagnetic emissions - Part 4: Measurement of conducted emissions - 1 ohm/150 ohm direct coupling method | EN IEC 61967-4 | -           |

| IEC 62132-1        | -<br>://stand | Integrated circuits - Measurement of electromagnetic immunity - Part 1: General conditions and definitions                                         | EN 62132-1     | -           |

| IEC 62132-4        | -             | Integrated circuits - Measurement of electromagnetic immunity 150 kHz to 1 GHz - Part 4: Direct RF power injection method                          | EN 62132-4     | -           |

| IEC 62215-3        | -             | Integrated circuits - Measurement of impulse immunity - Part 3: Non-synchronous transient injection method                                         | EN 62215-3     | -           |

| IEC 62228-1        | -             | Integrated circuits - EMC evaluation of transceivers - Part 1: General conditions and definitions                                                  | EN IEC 62228-1 | -           |

| ISO 7637-2         | -             | Road vehicles - Electrical disturbances from conduction and coupling - Part 2: Electrical transient conduction along supply lines only             | -              | -           |

| ISO 10605          | -             | Road vehicles - Test methods for electrical disturbances from electrostatic discharge                                                              | -              | -           |

**SIST EN IEC 62228-6:2023**

# iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST EN IEC 62228-6:2023

https://standards.iteh.ai/catalog/standards/sist/8b280d30-6ac7-4854-842d-40fce3dbcdc2/sist-en-iec-62228-6-2023

IEC 62228-6

Edition 1.0 2022-11

## INTERNATIONAL STANDARD

# NORME INTERNATIONALE

Integrated circuit – EMC evaluation of transceivers – Part 6: PSI5 transceivers

Circuits intégrés – Évaluation de la CEM des émetteurs-récepteurs – Partie 6: Émetteurs-récepteurs PSI5 C 62228-6:2023

https://standards.iteh.ai/catalog/standards/sist/8b280d30-6ac7-4854-842d-40fce3dbcdc2/sist-en-iec-62228-6-2023

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

ICS 31.200 ISBN 978-2-8322-6028-9

Warning! Make sure that you obtained this publication from an authorized distributor.

Attention! Veuillez vous assurer que vous avez obtenu cette publication via un distributeur agréé.

### CONTENTS

| F  | DREWO          | RD                                                                                                      | 5  |

|----|----------------|---------------------------------------------------------------------------------------------------------|----|

| 1  | Scop           | e                                                                                                       | 7  |

| 2  | Norm           | ative references                                                                                        | 7  |

| 3  | Term           | s, definitions and abbreviated terms                                                                    | 8  |

|    | 3.1            | Terms and definitions                                                                                   | 8  |

|    | 3.2            | Abbreviated terms                                                                                       |    |

| 4  | Gene           | ral                                                                                                     | 8  |

| 5  | Test           | and operating conditions                                                                                | 11 |

|    | 5.1            | Supply and ambient conditions                                                                           |    |

|    | 5.2            | Test operation modes                                                                                    |    |

|    | 5.3            | Test configuration                                                                                      |    |

|    | 5.3.1          | General test configuration for functional test                                                          |    |

|    | 5.3.2          | General test configuration for unpowered ESD test                                                       |    |

|    | 5.3.3          | Coupling ports for functional tests                                                                     | 14 |

|    | 5.3.4          | Coupling ports for unpowered ESD tests                                                                  |    |

|    | 5.4            | Test signals                                                                                            | 17 |

|    | 5.4.1          | General                                                                                                 |    |

|    | 5.4.2          | Test signals for Asynchronous mode                                                                      | 17 |

|    | 5.4.3          | Test signal for Synchronous parallel bus mode                                                           | 20 |

|    | 5.5            | Evaluation criteria                                                                                     | 21 |

|    | 5.5.1          | General                                                                                                 | 21 |

|    | 5.5.2          | Evaluation criteria in functional operation modes during exposure to disturbancesSISTENMEC.62228-622023 | 22 |

|    | 5.5.3          |                                                                                                         | 22 |

|    | 0.0.0          | disturbances of fee 3 dhedre 2/sistenties 62228-6-2023                                                  | 22 |

| 6  | Test           | and measurement                                                                                         | 23 |

|    | 6.1            | Emission of RF disturbances                                                                             | 23 |

|    | 6.1.1          | Test method                                                                                             | 23 |

|    | 6.1.2          | Test setup                                                                                              | 23 |

|    | 6.1.3          | Test procedure and parameters                                                                           | 25 |

|    | 6.2            | Immunity to RF disturbances                                                                             | 25 |

|    | 6.2.1          | Test method                                                                                             | 25 |

|    | 6.2.2          | Test setup                                                                                              | 25 |

|    | 6.2.3          | Test procedure and parameters                                                                           |    |

|    |                | Immunity to impulses                                                                                    |    |

|    | 6.3.1          | Test method                                                                                             |    |

|    | 6.3.2          | Test setup                                                                                              |    |

|    | 6.3.3          | Test procedure and parameters                                                                           |    |

|    | 6.4            | Electrostatic discharge (ESD)                                                                           |    |

|    | 6.4.1<br>6.4.2 | Test neture                                                                                             |    |

|    | 6.4.3          | Test setup  Test procedure and parameters                                                               |    |

| 7  |                | rest procedure and parameters                                                                           |    |

|    |                | normative) PSI5 test circuits                                                                           |    |

| ΑI | -              |                                                                                                         |    |

|    |                | General                                                                                                 |    |

|    | A.2<br>A.3     | Test circuit for emission and immunity tests on a PSI5 ECU IC                                           |    |

|    | Α.3            | Test circuit for emission and immunity tests on a PSI5 satellite IC                                     | ა9 |

| A.4 Test circuit for an unpowered ESD test on a PSI5 IC                                                       | 41 |

|---------------------------------------------------------------------------------------------------------------|----|

| Annex B (normative) Test circuit boards                                                                       | 43 |

| B.1 Test circuit board for emission and immunity tests                                                        | 43 |

| B.2 ESD test                                                                                                  | 43 |

| Annex C (informative) Examples of test limits for PSI5 transceiver in automotive applications                 | 44 |

| C.1 General                                                                                                   |    |

| C.2 Emission of RF disturbances                                                                               |    |

| C.3 Immunity to RF disturbances                                                                               | 45 |

| C.4 Immunity to Impulses                                                                                      | 48 |

| C.5 ESD                                                                                                       | 48 |

| Bibliography                                                                                                  | 49 |

| Figure 1 – PSI5 system overview                                                                               | 9  |

| Figure 2 – Example PSI5 wiring diagram with a single sensor and equivalent model                              | 10 |

| Figure 3 – PSI5-A configuration with a single sensor connection with two wires                                | 12 |

| Figure 4 – PSI5-P configuration with two sensor connection                                                    | 12 |

| Figure 5 – General test configuration for tests in functional operation modes                                 | 13 |

| Figure 6 – General test configuration for unpowered ESD test of an ECU IC                                     | 14 |

| Figure 7 – General test configuration for unpowered ESD test of a satellite IC                                | 14 |

| Figure 8 – Coupling ports for transceiver emission and immunity tests                                         |    |

| Figure 9 – Coupling ports for unpowered ESD tests                                                             |    |

| Figure 10 – Example drawing of the maximum deviation on an I-V characteristic                                 |    |

| SIST EN IEC 62228 6:2022                                                                                      |    |

| Figure 11 – Test setup for measurement of RF disturbances                                                     | 26 |

| Figure 13 – Test setup for impulse immunity tests                                                             |    |

| Figure 14 – Test setup for direct ESD tests                                                                   |    |

| -                                                                                                             | 33 |

| Figure A.1 – General circuit diagram of the PSI5 test network for emission and immunity tests on ECU IC       |    |

| Figure A.2 – General circuit diagram of the PSI5 test network for emission and immunity tests on Satellite IC |    |

| Figure A.3 – General circuit diagram of the PSI5 ECU IC for testing of direct ESD in unpowered mode           | 41 |

| Figure A.4 – General circuit diagram of the PSI5 sensor IC for testing of direct ESD in unpowered mode        |    |

| Figure C.1 – Example of limits for RF emission – PSI5 pins                                                    | 44 |

| Figure C.2 – Example of limits for RF emission – Other global pins                                            | 45 |

| Figure C.3 – Example of limits for RF immunity for functional status class A <sub>IC</sub> –                  |    |

| PSI5 pins                                                                                                     | 46 |

| Figure C.4 – Example of limits for RF immunity for functional status class A <sub>IC</sub> –                  |    |

| Other global pins                                                                                             | 46 |

| Figure C.5 – Example of limits for RF immunity for functional status class $C_{IC}$ or $D_{IC}$ -             |    |

| PSI5 pins                                                                                                     |    |

| Figure C.6 – Example of limits for RF immunity for functional status class $C_{IC}$ or $D_{IC}$ -             | _  |

| Other global pins                                                                                             | 47 |

| Table 1 – PSI5 physical layer electrical characteristics                                                                                                                                    | 9  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2 – Overview of required measurements and tests                                                                                                                                       | 10 |

| Table 3 – Supply and ambient conditions for functional operation                                                                                                                            | 11 |

| Table 4 – Sensor sink current specification                                                                                                                                                 | 13 |

| Table 5 – Definitions for component values of coupling ports for transceiver emission and immunity tests                                                                                    | 15 |

| Table 6 – Definitions of coupling ports for unpowered ESD tests                                                                                                                             | 17 |

| Table 7 – Communication test signal TX1 for Asynchronous mode (125 kbps)                                                                                                                    | 18 |

| Table 8 – Communication test signal TX2 for Asynchronous mode (189 kbps)                                                                                                                    | 19 |

| Table 9 – Communication test signal TX3 for Asynchronous low-power mode                                                                                                                     | 20 |

| Table 10 – Communication test signal TX4 for Synchronous parallel bus mode                                                                                                                  | 21 |

| Table 11 – Communication test signal TX5 for Synchronous parallel bus mode                                                                                                                  | 21 |

| Table 12 – Evaluation criteria for standalone and embedded PSI5 transceiver IC in functional operation modes                                                                                | 22 |

| Table 13 – Parameters for emission measurements                                                                                                                                             | 25 |

| Table 14 – Settings of the RF measurement equipment                                                                                                                                         | 25 |

| Table 15 – Specifications for DPI tests                                                                                                                                                     | 27 |

| Table 16 – Required DPI tests for functional status class A <sub>IC</sub> evaluation of Standard PSI5 transceiver ICs and embedded PSI5 transceiver ICs                                     | 28 |

| Table 17 – Required DPI tests for functional status class C <sub>IC</sub> or D <sub>IC</sub> evaluation of standard PSI5 transceiver ICs and ICs with embedded PSI5 transceiver             | 28 |

| Table 18 – Specifications for impulse immunity tests                                                                                                                                        | 30 |

| Table 19 – Parameters for impulse immunity test                                                                                                                                             | 31 |

| Table 20 – Required impulse immunity tests for functional status class A <sub>IC</sub> evaluation of standard and embedded PSI5 transceiver ICs                                             | 31 |

| Table 21 – Required impulse immunity tests for functional status class C <sub>IC</sub> or D <sub>IC</sub> evaluation of Standard PSI5 transceiver ICs and ICs with embedded PSI transceiver | 31 |

| Table 22 – Specifications for direct ESD tests                                                                                                                                              | 35 |

| Table B.1 – Parameter ESD test circuit board                                                                                                                                                | 43 |

| Table C.1 – Example of limits for impulse immunity for functional status class                                                                                                              | 40 |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

## INTEGRATED CIRCUIT – EMC EVALUATION OF TRANSCEIVERS –

Part 6: PSI5 transceivers

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

IEC 62228-6 has been prepared by subcommittee 47A: Integrated circuits, of IEC technical committee 47: Semiconductor devices. It is an International Standard.

The text of this International Standard is based on the following documents:

| Draft         | Report on voting |

|---------------|------------------|

| 47A/1145/FDIS | 47A/1147/RVD     |

Full information on the voting for its approval can be found in the report on voting indicated in the above table.

The language used for the development of this International Standard is English.

IEC 62228-6:2022 © IEC 2022

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available at <a href="https://www.iec.ch/members\_experts/refdocs">www.iec.ch/members\_experts/refdocs</a>. The main document types developed by IEC are described in greater detail at <a href="https://www.iec.ch/publications">www.iec.ch/publications</a>.

A list of all parts in the IEC 62228 series, published under the general title *Integrated circuit – EMC evaluation of transceivers*, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the stability date indicated on the IEC website under webstore.iec.ch in the data related to the specific document. At this date, the document will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

IMPORTANT – The "colour inside" logo on the cover page of this document indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

iTeh STANDARD PREVIEW (standards.iteh.ai)

SIST EN IEC 62228-6:2023

https://standards.iteh.ai/catalog/standards/sist/8b280d30-6ac7-4854-842d-40fce3dbcdc2/sist-en-iec-62228-6-2023

- 6 -

### INTEGRATED CIRCUIT – EMC EVALUATION OF TRANSCEIVERS –

Part 6: PSI5 transceivers

#### 1 Scope

This part of IEC 62228 specifies test and measurement methods for EMC evaluation of peripheral sensor interface 5 (PSI5) transceiver integrated circuits (ICs) under network condition. It defines test configurations, test conditions, test signals, failure criteria, test procedures, test setups and test boards. It is applicable for PSI5 satellite ICs (e.g. sensors) and ICs with embedded PSI5 transceivers (e.g. PSI5 electronic control unit IC). The document covers

- the emission of RF disturbances,

- the immunity against RF disturbances.

- · the immunity against impulses, and

- the immunity against electrostatic discharges (ESD).

#### 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 61967-1, Integrated circuits – Measurement of electromagnetic emissions – Part 1: General conditions and definitions

IEC 61967-4, Integrated circuits – Measurement of electromagnetic emissions – Part 4: Measurement of conducted emissions –  $1 \Omega / 150 \Omega$  direct coupling method

IEC 62132-1, Integrated circuits – Measurement of electromagnetic immunity – Part 1: General conditions and definitions

IEC 62132-4, Integrated circuits – Measurement of electromagnetic immunity 150 kHz to 1 GHz – Part 4: Direct RF power injection method

IEC 62215-3, Integrated circuits – Measurement of impulse immunity – Part 3: Non-synchronous transient injection method

IEC 62228-1, Integrated circuits – EMC evaluation of transceivers – Part 1: General conditions and definitions

ISO 7637-2, Road vehicles – Electrical disturbances from conduction and coupling – Part 2: Electrical transient conduction along supply lines only

ISO 10605, Road vehicles – Test methods for electrical disturbances from electrostatic discharge

IEC 62228-6:2022 © IEC 2022

### - 8 -

#### 3 Terms, definitions and abbreviated terms

For the purposes of this document, the terms and definitions given in IEC 61967-1, IEC 62132-1, IEC 62228-1, as well as the following apply.

ISO and IEC maintain terminology databases for use in standardization at the following addresses:

- IEC Electropedia: available at https://www.electropedia.org/

- ISO Online browsing platform: available at https://www.iso.org/obp

#### 3.1 Terms and definitions

#### 3.1.1

#### global pin

pin which carries a signal or power, which enters or leaves the application board without any active component in between

#### 3.1.2

#### mandatory components, pl

components needed for proper function and/or technical requirements of IC as specified by the IC manufacturer

#### 3.1.3

#### PSI5 satellite IC

PSI5 satellite or sensor transceiver with access to PSI5 signal

Note 1 to entry: A PSI5 satellite IC is a sensor device.

#### 3.1.4

#### IC with embedded PSI5 transceiver

IC with integrated PSI5 transceiver cell and PSI5 protocol handler with access to PSI5 signal

Note 1 to entry: An IC with an embedded PSI5 is an ECU device.

#### 3.2 Abbreviated terms

ASIC application specific integrated circuit

DPI direct RF power injection

DUT device under test

ECU electronic control unit

PCB printed circuit board

PSI5 peripheral sensor interface 5

TDMA time division multiple access

#### 4 General

The intention of this document is to evaluate the EMC performance of PSI5 transceiver ICs under application in minimal operating conditions (or in a minimal network). PSI5 transceiver ICs are in general available in two types: PSI5 satellite IC and IC with embedded PSI5 transceiver.

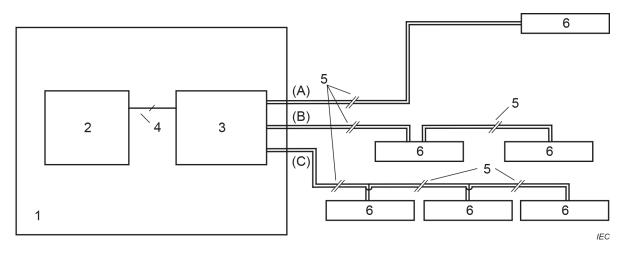

PSI5 transceiver system overview is shown in Figure 1.

#### Key

- 1 electronic control unit (ECU)

- 2 microcontroller

- 3 IC with embedded PSI5

- 4 digital interface

- 5 two wire current interface (PSI5)

- 6 PSI5 Sensor ICs

- (A) point-to-point topology

- (B) daisy-chain topology

- (C) bus topology

Figure 1 – PSI5 system overview

The sensors are connected to the ECU with two wires, using the same lines for power supply and data transmission. The IC with embedded PSI5 (e.g. transceiver ASIC in the ECU) provides a pre-regulated voltage to the sensors and reads in the transmitted sensor data.

The physical layer of PSI5 for EMC evaluation shall have the following characteristics, as shown in Table 1.

Table 1 – PSI5 physical layer electrical characteristics

| No.                                                                                                              | Parameter                              | Variable                                 | Minimum | Typical | Maximum | Unit |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------------------------------|---------|---------|---------|------|

| 1                                                                                                                | Supply voltage                         | $V_{\mathrm{SSmax}}, V_{\mathrm{CEmax}}$ | 4       |         | 16,5    | V    |

| 2                                                                                                                | Reverse polarity protection (standard) | <i>t</i> < 80 ms                         | -105    |         |         | mA   |

| 3                                                                                                                | Reverse polarity protection (extended) | <i>t</i> < 50 ms                         | -130    |         |         | mA   |

| 4                                                                                                                | Internal ECU resistance                | R <sub>E1</sub>                          | 9       |         | 10      | Ω    |

| 5                                                                                                                | PSI5 ECU filter capacitor <sup>a</sup> | $C_{E}$                                  | 9       | 10      | 11      | nF   |

| 6                                                                                                                | PSI5 ECU filter resistor               | R <sub>E2</sub>                          | 2       | 2,2     | 2,5     | Ω    |

| 7                                                                                                                | PSI5 ECU filter capacitor <sup>a</sup> | $C_{L}$                                  | 9       | 10      | 11      | nF   |

| $^{\rm a}$ $$ Symmetrical values for $C_{\rm E}$ and $C_{\rm L}$ are proposed to have a balanced filter on PSI5. |                                        |                                          |         |         |         |      |

An example of the typical PSI5 network, with a single sensor and the equivalent model, is shown in Figure 2. Most implementations will have a mandatory PSI5 ECU filter (PSI5 bus filter) used on the ECU side as shown in Figure 2. Sensor side may also have additional filter components as per the IC manufacturer specifications.