## NORME INTERNATIONALE INTERNATIONAL STANDARD

CEI IEC 60821

1991

AMENDEMENT 1

AMENDMENT 1

1999-01

Amendment 1

VMEbus – Microprocessor system bus for 1 byte to 4 byte data

### iTeh STANDARD PREVIEW

Amendementdards.iteh.ai)

Bus VMEbus —

HE 60821:1991/AMD1:1999

Bus systeme a microprocesseurs

pour données de 1 octet à 4 octets

© IEC 1999 Droits de reproduction réservés — Copyright - all rights reserved

International Electrotechnical Commission 3, rue de Varembé Geneva, Switzerland Telefax: +41 22 919 0300 e-mail: inmail@iec.ch IEC web site http://www.iec.ch

CODE PRIX

PRICE CODE

J

#### **FOREWORD**

This amendment has been prepared by subcommittee 26: Microprocessor systems, of the Joint Technical Committee ISO/IEC JTC 1: Information technology.

The text of this amendment is based on the following documents:

| Text                     | Report on voting         |

|--------------------------|--------------------------|

| ISO/IEC JTC1/SC 26 N 237 | ISO/IEC JTC1/SC 26 N 218 |

Full information the voting for the approval of this amendment can be found in the report on voting indicated in the above table.

#### **CHAPTER 2: IEC 60821 BUS DATA TRANSFER BUS**

Page 67

#### 2.2.4.5 WRITE\*

Replace the first sentence of this subclause by the following:

(standards.iteh.ai)

WRITE\* is a level significant signal line that is strobed by the falling edge of the first data strobe (DSA\*) and is valid as long as any data strobe (DSA\* or DSB\*) is low.

https://standards.iteh.ai/catalog/standards/sist/49366dbc-cb25-4223-83f0-8e83ca407a46/iec-60821-1991-amd1-1999

Page 89

#### 2.3.6 Basic data transfer capabilities

Replace Rule 2.65 by the following:

D08(O) SLAVES MUST NOT respond by driving DTACK\* low during cycles that request access to byte locations BYTE(0), BYTE(2), BYTE(1-2), BYTE(2-3), BYTE(0-2), BYTE(1-3), or BYTE(0-3).

Insert, at the end of Suggestion 2.8, the following text:

4) When a D08(O) SLAVE is requested to do a BYTE(0) or BYTE(2) transfer.

Page 93

Table 2-10 – Mnemonics that specify basic data transfer capabilities

Replace in the third column the words "can accept" and "can monitor" by "must accept" and "must monitor".

#### 2.3.7 Block transfer capabilities

Add, on page 95, at the end of Rule 2.12, the words "in the address space."

Replace, on page 97, at the end of the first sentence of Observation 2.87, "D08-D15" by "D00-D15".

Page 99

Table 2-11 – Mnemonic that specifies block transfer capabilities

Replace, in the third column, the words "Can accept" and "Can monitor" by "Must accept" and "Must monitor".

Page 101

Table 2-12 – Mnemonic that specifies read-modify-write capabilities

Replace, in the third column, the words "Can accept" and "Can monitor" by "Must accept" and "Must monitor".

#### Page 103

Page 105

# iTeh STANDARD PREVIEW (standards.iteh.ai)

#### 2.3.9 Unaligned transfer capabilities

IEC 60821:1991/AMD1:1999

https://standards.iteh.ai/catalog/standards/sist/49366dbc-cb25-4223-83f0-8e83ca407a46/iec-60821-1991-amd1-1999

Table 2-13 – Transferring 32 bits of data using multiple byte transfer cycles

Replace, in row B, line 3, and line 6, "Group 1, BYTE(0)" by "GROUP 2, BYTE(0)".

Replace, in row D, line 6, "D00-D23" by "D00-D07".

Page 107

Table 2-14 – Transferring 16 bits of data using multiple byte transfer cycles

Replace, in row F, line 1, "D08-D15" by "D00-D07".

Replace, in row F, line 2, "D16-D23" by "D08-D15".

#### **RULE 2.6**

Replace, at the beginning of the sentence, "D08(0)" by "D08(O)"

Replace the text before table 2-15 and after RULE 2.6 by:

Table 2-15 lists how the unaligned transfer (UAT) mnemonic is used to describe MASTERS and SLAVES.

Table 2-15 – Mnemonic that specifies unaligned transfer capability

Replace table 2-15 by the following revised table:

| The following mnemonic | When applied to a | Means that it                                                   |

|------------------------|-------------------|-----------------------------------------------------------------|

| UAT                    | D32 MASTER        | Can generate the following cycles:                              |

|                        | D32 SLAVE         | MUST accept the following cycles:                               |

|                        |                   | Quad byte read cycles:<br>BYTE(0-3) READ                        |

|                        |                   | Quad byte write cycle:<br>BYTE (0-3) WRITE                      |

|                        |                   | Triple byte read cycles:<br>BYTE(0-3) READ<br>BYTE(1-3) READ    |

|                        |                   | Triple byte write cycles:<br>BYTE(0-2) WRITE<br>BYTE(1-3) WRITE |

|                        |                   | Double byte read cycles:<br>BYTE(1-2) READ                      |

|                        |                   | Double byte write cycles:<br>BYTE(1-2) WRITE                    |

# iTeh STANDARD PREVIEW (standards.iteh.ai)

Table 2-16 - Mnemonic that specifies ADDRESS-ONLY capability

$\label{lem:https://standards.itch.ai/catalog/standards/sist/49366dbc-cb25-4223-83f0-Replace, in the first column, "ADO" by 7ADQ" 60821-1991-amd1-1999$

Page 133

Page 109

Table 2-17 - Timing diagrams that define MASTER, SLAVE and LOCATION MONITOR operation

Replace, in the first row of the first column, "ADO" by "ADO".

Page 135

Table 2-18 – Definitions of mnemonics used in tables 2-19, 2-20 and 2-21

Replace, in the seventh row, "DRIVEN BY SLAVE" by "DRIVEN BY SLAVE?".

Page 139

Table 2-20 – Use of DS1\*, DS0\*, AO1 and LWORD\* during the various cycles

Replace, in the first row, "ADO" by "ADO".

Page 141

Table 2-21 – Use of the data lines to transfer data

Replace, in the first row, "AD0" by "ADO".

#### **CHAPTER 3: IEC 60821 BUS DATA TRANSFER BUS ARBITRATION**

Page 213

#### 3.3.1 ARBITER

Replace, on page 215, in the first sentence of the eighth paragraph, "BRO\*" by "BRO\*" and "BGOIN\*" by "BG0IN\*".

Page 221

#### 3.3.2 REQUESTER

Replace, on page 225, RULE 3.14 by the following:

After having been granted the bus, the FAIR ARBITER MUST monitor its bus request line and it MUST NOT issue a new bus request until its bus request line has once been high.

#### iTeh STANDARD PREVIEW

## CHAPTER 4: IEC 60821 BUS PRIORITY INTERRUPT BUSII)

Page 259

IEC 60821:1991/AMD1:1999

**4.2.1** Interrupt requestatines s.iteh.ai/catalog/standards/sist/49366dbc-cb25-4223-83f0-8e83ca407a46/iec-60821-1991-amd1-1999

Replace the title of this subclause by the following new title:

Interrupt request lines - IRQ1\* - IRQ7\*

#### 4.2.2 Interrupt acknowledge line

Replace the title of this subclause by the following new title:

Interrupt acknowledge line - IACK\*

Page 261

#### 4.3 Priority Interrupt Bus modules - Basic description

Replace, in the first sentence of the first paragraph, "IACK\*" by "IACK".

Replace, in the first sentence of the second paragraph, "IACK\*" by "IACK".

Page 275

Table 4-2 – INTERRUPTERS: RULES and PERMISSIONS for driving and monitoring the dotted lines

Replace, in the second and in the last row, "MAY or MAY NOT" by "MAY".

Page 281

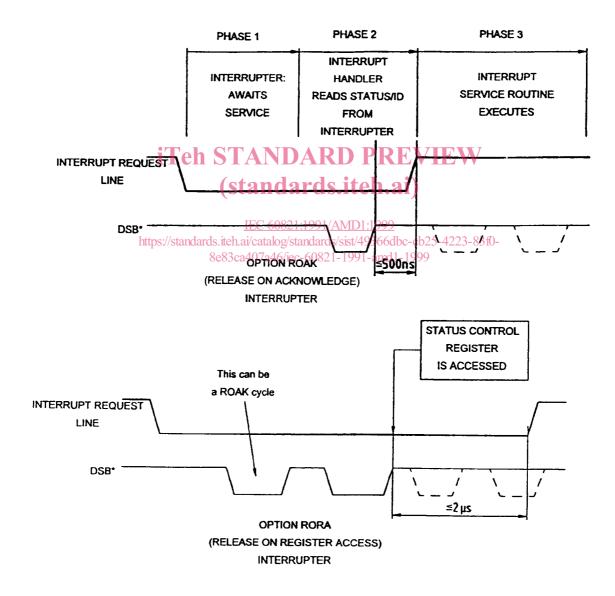

#### 4.3.7 Interrupt release capabilities

Replace, on page 283, in the second line of Rule 4.5, and the second line of Rule 4.6, "before DSA\* has fallen" by "before it detects a falling edge on DSA\*".

Page 285

Figure 4-8

Replace figure 4-8 by the following new figure:

Figure 4-8 – Release of the interrupt request lines by ROAK and RORA INTERRUPTERS

#### **CHAPTER 7: IEC 60821 BUS MECHANICAL SPECIFICATIONS**

Page 415

#### 7.2 IEC 60821 BUS boards

Replace RECOMMENDATION 7.1 by the following new RECOMMENDATION 7.1:

Make IEC 60821 BUS boards 1,6 mm  $\pm$  0,2 mm (0,063 in  $\pm$  0,008 in) thick.

Page 439

Figure 7-2

Replace RULE 7.32 by the following new RULE 7.32:

Boards MUST be 1,6 mm  $\pm$  0,2 mm (0,063 in  $\pm$  0,008 in) thick in the guide area.

Page 441

Figure 7-3

Replace RULE 7.33 by the following new RULE 7.33:

Boards MUST be 1,6 mm  $\pm$  0,2 mm (0,063 in  $\pm$  0,008 in) thick in the guide area.

Page 465

Page 481

iTeh STANDARD PREVIEW (standards.iteh.ai)

Figure 7-15

Replace, in PERMISSION 7.24, "J<sub>1</sub> or a J<sub>2</sub>" by J<sub>1</sub>/J<sub>2</sub>" 1:1999

https://standards.iteh.ai/catalog/standards/sist/49366dbc-cb25-4223-83f0-8e83ca407a46/iec-60821-1991-amd1-1999

#### Appendix A - Glossary of IEC 60821 bus terms

Add, under the title of this appendix, the term "normative".

Replace, in the sixth paragraph, the title "ADO" by "ADO".

Page 493

#### Appendix B – IEC 60821 bus connector/pin description

Add, under the title of this appendix, the term "normative".

Page 499

#### Appendix C – Use of the SERCLK and SERDAT\* lines

Add, under the title of this appendix, the term "informative".

Page 503

#### Appendix D - Metastability and resynchronisation

Add, under the title of this appendix, the term "informative".

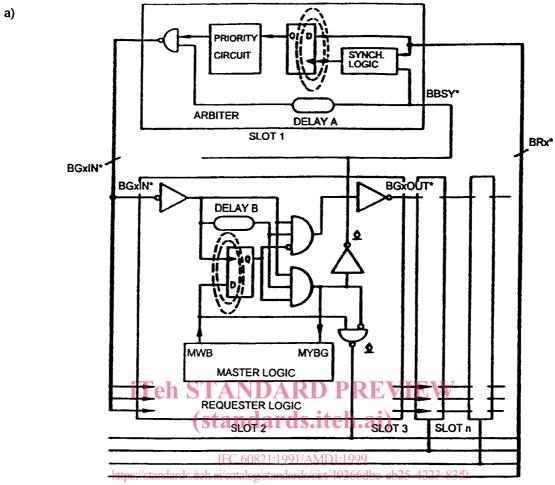

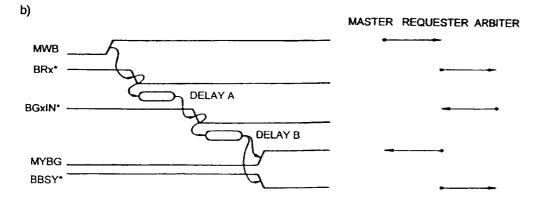

Replace, on page 527, figure D-5 by the following new figure:

8e83ca407a46/iec-60821-1991-amd1-1999

Figure D-5 - VMEbus arbitration structure; dashed circles indicate where critical input conditions can arise

a) simplified block diagram;

b) control signals, with evidence of the handshake loop

(MASTER - REQUESTER - ARBITER - REQUESTER - MASTER)

Page 539

#### D.6.4 Asynchronous ARBITER

Replace the third sentence of the second paragraph by the following new text:

The delay of "F" should be calculated to cover the metastable resolution time of "E" at the selected MTBF, plus the total propagation of the GRANT LOGIC block as described in section D.5.

Page 541

#### **D.7 Conclusions**

Delete the last paragraph of this clause.

Page 545

#### Appendix E - Permissible capability subsets

Add, under the title of this appendix, the term "normative".

### Page 547 iTeh STANDARD PREVIEW

## E.2.1.2 Address-Only cycles (standards.iteh.ai)

Replace, in the first sentence of the first paragraph, in the first sentence of the second paragraph, and in the second sentence ("ADO" by "ADO" 1999

https://standards.iteh.ai/catalog/standards/sist/49366dbc-cb25-4223-83f0-

Table E-1 – Permissible subsets of addressing capabilities 11-1999

Replace, in the right-hand column, "ADO" by "ADO".

Page 551

#### E.2.2.4 Read-modify-write capability

Table E.3 – MASTER: Permissible subsets of data transfer capabilities

Replace, on page 553, in the first row, "MALL16" by "MALL8".

Table E.4 – SLAVE: Permissible subsets of data transfer capabilities

Insert, on page 553, in column D08(O), the character "X" throughout the column.

Table E.5 – LOCATION MONITOR: Permissible subsets of data transfer detection capabilities

Delete, on page 555, in column UAT, row LMRMW32, the character "X".

Insert, on page 555, in column UAT, row LMALL32 + UAT, the character "X".