# INTERNATIONAL STANDARD

### IEC 62137

First edition 2004-07

Environmental and endurance testing

Test methods for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and OFN

iTextonia of testing

the surface-mount boards

of testing

the sur

#### **Publication numbering**

As from 1 January 1997 all IEC publications are issued with a designation in the 60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

#### Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example, edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the base publication incorporating amendment 1 and the base publication incorporating amendments 1 and 2.

#### Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC, thus ensuring that the content reflects current technology. Information relating to this publication, including its validity, is available in the IEC catalogue of publications (see below) in addition to new editions, amendments and corrigenda. Information on the subjects under consideration and work in progress undertaken by the technical committee which has prepared this publication, as well as the list of publications issued, is also available from the following:

• IEC Web Site (<u>www.iec.ch</u>)

#### . Catalogue of IEC publications

The on-line catalogue on the IEC web site (www.iec.ch/search.ub) enables you to search by a variety of criteria including text searches technical committees and date of publication. On-line information is also available on recently issued publications, withdrawn and replaced publications, as well as corrigenda.

#### IEC Just Published

This summary of recently issued publications (<a href="https://www.iec.ch/online\_news/justpub">www.iec.ch/online\_news/justpub</a>) is also available by email. Please contact the customer Service Centre (see below) for (urther information.

Customer Service Centre

If you have any questions regarding this publication or need further assistance, please contact the Customer Service Centre:

Email: <u>custserv@iec.sb/</u>

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

# INTERNATIONAL STANDARD

### IEC 62137

First edition 2004-07

Environmental and endurance testing

Test methods for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

Current Preview

5//standards.iteh.xi

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iTelegraphy iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

FLGA, LGA, SON and QFN

iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

iteh.ai

current for surface-mount boards

of area array type packages FBGA, BGA,

iteh.ai

current for surface-mount boards

of area array type packages FBGA,

iteh.ai

current for surface-mount boards

of area array type packages FBGA,

iteh.ai

current for surface-mount boards

of area array type packages FBGA,

iteh.ai

curre

© IEC 2004 — Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

PRICE CODE

#### CONTENTS

| FO                                  | OREWORD                                                                     | 3                        |

|-------------------------------------|-----------------------------------------------------------------------------|--------------------------|

| 1                                   | Scope                                                                       | 5                        |

| 2                                   | Normative references                                                        | 5                        |

| 3                                   | Terms and definitions                                                       |                          |

| 4                                   | Abbreviations                                                               |                          |

| 5 Solder joint quality test methods |                                                                             | 6                        |

|                                     | 5.1 Reflow solderability test for solder joint                              |                          |

|                                     | 5.2 Reserved for future use                                                 | 9                        |

| 3                                   | 5.2 Reserved for future use                                                 | 9                        |

|                                     | 6.1 Bending test for solder joint                                           | 9                        |

|                                     | 6.2 Uron test for solder joint                                              | \ \ / 9                  |

| 7                                   | Environment test methods                                                    | 9                        |

|                                     | 7.1 Temperature cycling test for solder joint                               | ·/9                      |

|                                     | 7.2 Reserved for future use                                                 | 12                       |

|                                     |                                                                             |                          |

| An                                  | nnex A (informative) Informative test methods for test board - Guidance.    | 13                       |

| An                                  | nnex B (informative) Standard mounting process for area array type pack     | ages and                 |

| pe                                  | eripheral terminal type packages (QFN and SON)                              | 23                       |

|                                     |                                                                             |                          |

| 3it                                 | ibliography                                                                 | 26                       |

|                                     | igure 1 - Temperature measurement of the specimen using thermocouple        |                          |

| Fig                                 | gure 2 – Moistening/reflow process cycle proposed                           | 8                        |

| Fig                                 | gure 2 – Moistening/reflow process cycle proposed                           | -/d1388d/1ec-0213/-<br>8 |

|                                     | gure 4 – Configuration of one cycle period                                  |                          |

|                                     | igure A.1 – Temperature measurement of the specimen using thermocoup        |                          |

|                                     | igure A.2 – Temperature measurement of the specimen using thermocour        |                          |

| _                                   | gure A.3 – Measuring method for peel strength                               |                          |

|                                     | gure A.4 – Standard land shape of the mount reliability test board          |                          |

| _                                   | igure A.5 – Design standard for land shape of packages of peripheral term   |                          |

|                                     | ON and QFN                                                                  |                          |

|                                     |                                                                             |                          |

| Та                                  | able 1 – Temperature cycling test conditions                                | 11                       |

| Га                                  | able A.1 - Types of mount reliability test board                            | 20                       |

| Та                                  | able A.2 – Standard mount reliability test board layer configuration        | 21                       |

|                                     | able A.3 – Design guideline for land size of packages of area array ball/la |                          |

|                                     | GA, FBGA, LGA, and FLGA                                                     |                          |

|                                     | able B.1 – Stencil design standard for area array terminal type packages.   |                          |

| Та                                  | able B.2 – Stencil design standard for peripheral terminal type packages .  | 24                       |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

## ENVIRONMENTAL AND ENDURANCE TESTING – TEST METHODS FOR SURFACE-MOUNT BOARDS OF AREA ARRAY TYPE PACKAGES FBGA, BGA, FLGA, LGA, SON AND QFN¹

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (behavior referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as hearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, EC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an EC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62137 has been prepared by IEC technical committee 91: Electronics assembly technology.

The text of this standard is based on the following documents:

| FDIS        | Report on voting |

|-------------|------------------|

| 91/444/FDIS | 91/451/RVD       |

Full information on the voting for the approval of this standard can be found in the report on voting indicated in the above table.

BGA ball grid array

FLGA fine-pitch land grid array

LGA land grid array

SON small outline non-leaded package QFN quad flat-pack non-leaded package

<sup>1</sup> FBGA fine-pitch ball grid array

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- · reconfirmed;

- withdrawn;

- · replaced by a revised edition, or

- amended.

## ENVIRONMENTAL AND ENDURANCE TESTING – TEST METHODS FOR SURFACE-MOUNT BOARDS OF AREA ARRAY TYPE PACKAGES FBGA, BGA, FLGA, LGA, SON AND QFN

#### 1 Scope

This International Standard specifies the test method and guidelines for evaluating the quality and reliability of boards, solder lands, solder process and solder joints of reflow solder mounted area array type packages and peripheral terminal type packages.

This standard tests for durability against mechanical and thermal stress received during or after the mounting process of discrete semiconductor devices and of integrated circuits (hereinafter both referred to as semiconductor devices) used mainly for industrial and consumer use equipment.

The test method specified in this standard is an integrated one by including the evaluation method of mounting methods, mounting conditions, printed circuit boards, soldering materials, and so on. It does not specify the evaluation method of the individual semiconductor devices.

Mounting conditions, printed wiring boards, soldering materials, and so on significantly affect the result of the test specified in this standard. Therefore, the test specified in this standard shall not be regarded as the one to be used to guarantee the mounting reliability of the semiconductor devices.

The test method is not necessary if there is no stress (mechanical or others) from any of the tests covered in this standard.

#### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60068-1:1988, Environmental testing - Part 1: General and guidance

IEC 60191-6-2:2001 Mechanical standardization of semiconductor devices — Part 6-2: General rules for the preparation of outline drawings of surface mounted semiconductor device packages — Design guide for 1,50 mm, 1,27 mm and 1,00 mm pitch ball and column terminal packages

IEC 60191-6-5:2004, Mechanical standardization of semiconductor devices – Part 6-5: General rules for the preparation of outline drawings of surface mounted semiconductor device packages – Design guide for fine-pitch ball grid array (FBGA)

IEC 61190-1-1, Attachment materials for electronic assemblies – Part 1-1: Requirements for soldering fluxes for high-quality interconnections in electronics assembly

IEC 61190-1-2, Attachment materials for electronic assemblies – Part 1-2: Requirements for solder pastes for high-quality interconnections in electronics assembly

IEC 61190-1-3, Attachment materials for electronic assemblies – Part 1-3: Requirements for electronic grade solder alloys and fluxed and non-fluxed solid solders for electronic soldering applications

JEITA<sup>2</sup> ETR-7001:1998, Terms and definitions for surface mount technology

<sup>&</sup>lt;sup>2</sup> Japan Electronics and Information Technology Industries Association.

#### 3 Terms and definitions

For the purposes of this document, the terms and definitions for BGA, FBGA and so on, are referred to in IEC 60191-6-2 and IEC 60191-6-5.

#### 4 Abbreviations

FBGA fine-pitch ball grid array

BGA ball grid array

FLGA fine-pitch land grid array

LGA land grid array

SON small outline non-leaded package

QFN quad flat-pack non-leaded package

#### 5 Solder joint quality test methods

#### 5.1 Reflow solderability test for solder joint

#### 5.1.1 Purpose

This test method specifies the reflow solderability test for the solder joint, as part of the specification in the standard. It is used to evaluate the solderability of reflow soldering of area-array type packages and peripheral terminal type packages (QFN and SON).

#### 5.1.2 Test specimen

The test specimen shall satisfy the following conditions:

- a) test board design (see Clause A.4);

- b) standard mounting process (see Annex B);

- c) resistance to reflow soldering (see Clause A.1), solderability test for test board land (see Clause A.2) and peel test method for test board land (see Clause A.3).

#### 5.1.3 Test apparatus

The test apparatus shall include the following:

a) Oven

The oven shall maintain the temperature specified in 5.1.4.2.

b) Moistening equipment

The humidifier shall maintain the temperature and humidity specified in 5.1.4.2. No reaction shall occur to the material of the oven at high temperatures. The water used for the test shall be purified water or deionized water, with pH 6,0 to pH 7,2 at 23  $^{\circ}$ C, and with a resistivity of 500  $\Omega$ m or higher.

c) Infrared reflow/air reflow furnace

The infrared reflow/air reflow furnace shall meet the heating process conditions specified in 5.1.4.4.

#### 5.1.4 Test procedure

#### 5.1.4.1 Initial measurement

The initial measurement shall be carried out according to the items and conditions specified in the individual standard.

#### 5.1.4.2 Moisture treatment

The moisture treatment is desirable for the test because a soldering defect may occur with moisture. "Defect of soldering" is defined in ETR-7001 as general failure of soldering.

#### a) Pre-treatment

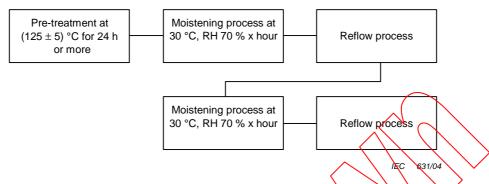

Unless otherwise specified in the individual standard, the specimen subject to the moistening reflow pre-treatment in b) shall be baked in the oven at (125 ± 5) °C for 24 h or more

#### b) Moistening process (1)

The specimen shall be moistened as specified in the individual standard. If there is no such specification mentioned in the individual standard, the specimen shall be subject to the moistening condition at 30 °C, with a relative humidity of 70% for 96 h.

#### c) Moistening process (2)

When the specimen is subjected to the reflow process twice, the specimen reflow soldered on the test board shall be moistened once again under the moistening condition as specified in the individual standard.

In this case, by taking into consideration the moistening reflow characteristic of the test board, it is desirable to set both the moisture soaking conditions and the moistening time for the repeat version of the test. In general, it is desirable to set the moistening condition to 30 °C, with a relative humidity of 70 %, or to 30 °C, with a relative humidity of 85 % up to 165 h maximum.

#### 5.1.4.3 Test conditions

#### a) Reflow profile measurement

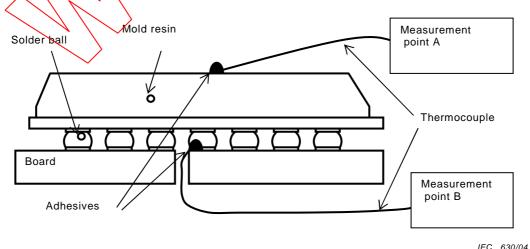

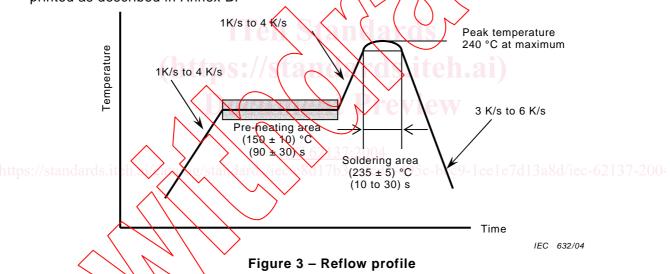

The infrared reflow/air reflow furnace shall meet the heating process conditions specified in Figure 3. The temperature of the specimen shall be measured at measurement Point A (the centre on the top of the package) and measurement point B (the soldered inner part of the terminal), shown in Figure 1.

Figure 1 – Temperature measurement of the specimen using thermocouples

#### b) Test process.

The board to be tested shall carry out the evaluation under similar conditions to that of the actual usage of the board.

A proposal is shown in Figure 2.

Figure 2 - Moistening/reflow process cycle proposed

#### 5.1.4.4 Reflow heating

Mount the specimen on the mount reliability test board on which the solder paste has been printed as described in Annex B.

#### 5.1.4.5 Post-treatment

After the test has been completed, if necessary, leave the specimen in the standard condition for the time specified in the individual standard:

- standard temperature range: 15 °C to 35 °C;

- standard relative humidity: 25 % to 75 %;

- standard atmospheric pressure: 86 kPa to 106 kPa.

Refer to IEC 60068-1.

#### 5.1.4.6 Evaluation

Measure the electrical characteristic of the specimen according to the individual standard. Then, using soft X-ray inspection equipment, check the soldered condition. If necessary, observe the cross-sectional view after the buried process of resin.

#### 5.2 Reserved for future use

(Vacant).

#### 6 Mechanical test methods

#### 6.1 Bending test for solder joint

(Under consideration)

#### 6.2 Drop test for solder joint

(Under consideration)

#### 7 Environment test methods

#### 7.1 Temperature cycling test for solder joint

#### 7.1.1 Purpose

This test method specifies the temperature cycling test for solder joints. It is an accelerated test method to measure the life expectancy of semiconductor devices and of the solder joint on the board by taking into consideration the assumed temperature increase when area array type packages and peripheral terminal type packages (QFN and SON) mounted on the board are working.

#### 7.1.2 Test specimen

The test specimen shall satisfy the following conditions:

- a) test board design (see Clause A.4);

- b) standard mounting process (see Annex B);

- c) reflow solderability (see 5.1), solderability test for test board land (see Clause A.2), and peel test method for test board land (see Clause A.3).

#### 7.1.3 Test apparatus

The test apparatus shall include the following:

a) Oven

The oven shall maintain the temperature specified in 7.1.4.2.

b) Moistening equipment

The humidifier shall maintain the temperature and humidity as specified in 7.1.4.2. No reaction shall occur in the material of the oven at high temperatures. The water used for the test shall be purified water or deionized water, with pH 6,0 to pH 7,2 at 23  $^{\circ}$ C, and with a resistivity of 500  $\Omega$ m or higher.

c) Temperature cycling test oven

The temperature cycling test oven shall be of vapour phase type that meets the test conditions of the temperature cycle profile specified in 7.1.4.3.

#### 7.1.4 Test procedure

#### 7.1.4.1 Initial measurement

The initial measurement shall be carried out according to the items and conditions specified in the individual standard.